Шина I

Шина Inter 1C Bus (шина соединения микросхем), или, кратко, PC, — синхронная последовательная шина, обеспечивающая двустороннюю передачу данных между подключенными устройствами. Шина ориентирована на 8-битные передачи. Передача данных может быть как одноадресной, к выбранному устройству, так и широковещательной. Уровни сигналов — стандартные, совместимые с широко распространенной логикой ТТЛ, КМОП, N-МОП, как с традиционным питанием +5 В, так и с низковольтным (3,3 В и ниже). Микросхемы с интерфейсом PC, как правило, имеют аппаратную поддержку протокольных функций. Протокол позволяет взаимодействовать на одной шине устройствам с различным быстродействием интерфейса. Требования к временным параметрам сигналов весьма свободные, так что на компьютерах и микроконтроллерах, не имеющих аппаратной поддержки шины PC, ее протокол может быть реализован даже чисто программно.

Шина PC используется уже давно, ее официальная версия 1.0 вышла в 1992 г. По сравнению с предшествующими (черновыми) версиями, здесь отсутствует (как запутанная и неиспользуемая) возможность программного задания адреса ведомого устройства. Также отсутствует низкоскоростной режим (Low speed), являющийся частным случаем стандартного режима — Standard Mode (5) — со скоростью 0-100 Кбит/с. В версии 1.0 появились определение быстрого режима — Fast Mode (F) — со скоростью 0-400 Кбит/с и связанные с ним изменения требований к форме сигнала и фильтрации помех. Также здесь веден режим 10-битной адресации устройств. Версия 2.0 вышла в 1998 г., когда интерфейс PC стал фактиче-

422 Глава 11. Вспомогательные последовательные интерфейсы и шины

В версии 2.1 (2000 г.) уточнены некоторые моменты, касающиеся временных диаграмм в режиме Hs. Приведенная здесь информация основана на спецификации шины PC версии 2.1, доступной на сайте www.philips.com. Параметры интерфейсных сигналов приводятся в п. 11.1.4, где они сопоставляются с требованиями SMBus и ACCESS.Bus.

Интерфейс PC использует две сигнальные линии: данных SDA (Serial Data) и синхронизации SCL (Serial Clock). В обменах участвуют два устройства — ведущее (master) и ведомое (slave). Ведущее и ведомое устройства могут выступать в роли и передатчика, и приемника данных. Протокол допускает наличие на шине нескольких ведущих устройств и имеет простой механизм арбитража (разрешения коллизий).

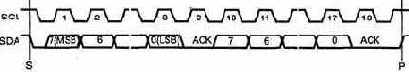

Протокол обмена для обычных устройств F/S иллюстрирует рис. 11.1. Обе сигнальные линии имеют нагрузочные резисторы, «подтягивающие» их уровень к напряжению питания. На устройстве к каждой линии подключен приемник и передатчик типа «открытый коллектор» («открытый сток»), у ведомого устройства передатчик на линии SCL не обязателен. Все одноименные передатчики соединяются по схеме «Монтажное И»: уровень в линии будет высоким, если все передатчики пассивны, и низким, если хоть у одного передатчика выходной транзистор открыт. В покое (Idle, исходное состояние шины) все передатчики пассивны. Синхронизацию задает ведущее устройство, но ведомое, если оно не имеет достаточного быстродействия, может замедлять обмен данными.

Рис. 11.1. Протокол передачи данных I2C

Начало любой передачи — условие Start — инициируется ведущим устройством, убедившимся в том, что шина свободна (высокий уровень сигналов SCL и SDA). Условие Start (на диаграммах обозначается как S)— перевод сигнала SDA из высокого в низкий при высоком уровне SCL Завершается операция переводом сигнала SDA из низкого уровня в высокий при высоком уровне SCL — условие Stop (обозначается как Р), также вводящееся ведущим устройством. При передаче данных состояние линии SDA может изменяться только при низком уровне SCL, биты данных считаются действительными во время высокого уровня SCL Ведущее устройство может начать очередную передачу вслед за текущей, не вводя условие

11.1. Последовательные шины на базе I2C_______________________________ 423

Stop, — это называется repeated Start (повторный старт, обозначающийся S г). В протоколе условия S и Sr почти равнозначны. Каждая посылка данных состоит из 8 бит данных, формируемых передатчиком (старший бит — MSB — передается первым), после чего передатчик на один такт освобождает линию данных для получения подтверждения. Приемник во время девятого такта формирует бит подтверждения Ac k, по которому передатчик убеждается, что его «услышали». После передачи бита подтверждения ведомое устройство может задержать следующую посылку, удерживая линию SCL на низком уровне. Ведомое устройство в режимах F/S может замедлить передачу по шине и на уровне приема каждого бита, удерживая SCL на низком уровне после его спада, сформированного передатчиком. Поэтому ведущее устройство должно генерировать сигнал SCL не «вслепую», а анализируя состояние линии SCL: сняв этот сигнал, новый импульс (открытие ключа передатчика) оно имеет право вводить, лишь убедившись, что сигнал SCL вернулся в пассивное состояние (высокий уровень). В противном случае синхронизация будет потеряна. Сигнал SCL может быть растянут и другим устройством, пытающимся захватить шину в это же время. Тактовый сигнал SCL не обязательно будет равномерным: время его нахождения на низком уровне будет определяться максимальным временем, в котором его захочет удержать самое медленное из устройств, участвующих в данном обмене (даже и конфликтующих); время нахождение на высоком уровне будет определяться самым быстрым из конфликтующих ведущих устройств.

Коллизия (конфликт) на шине может возникнуть, когда два (или более) устройства, убедившись в покое шины, одновременно (или почти одновременно) инициируют обмен данными. Все они управляют линиями SCL и SDA и наблюдают за ними. Если устройство, передающее единицу (высокий уровень), в данном такте на линии SDA видит ноль (низкий уровень), оно должно признать свой проигрыш в конфликте и освободить линии SCL и SDA (при этом ему позволительно управлять линией SCL до конца передачи текущего байта).

Выигравшее устройство даже и не заметит проигравших конкурентов и продолжит работу. Арбитраж может закончиться в любом месте посылки, формируемой ведущим устройством. Искажения информации, передаваемой выигравшим устройством, не происходит (приятное отличие от коллизий в сетях Ethernet). Если ведущее устройство, проигравшее в конфликте, имеет и функции ведомого устройства, по признанию проигрыша оно должно перейти в режим ведомого, поскольку конфликт мог быть вызван и попыткой обращения к нему победившего ведущего устройства.

Бит подтверждения АС К, вводящийся в конце каждого байта устройством-приемником, выполняет несколько функций. Когда передатчиком является ведущее устройство, приемник (ведомый) должен вводить нулевой бит АС К, свидетельствующий о нормальном получении очередного байта. Единичный бит АС К (нет подтверждения) в ответ на посылку адреса свидетельствует об отсутствии адресованного ведомого устройства на шине или его занятости внутренними процессами. Отсутствие подтверждения байта данных свидетельствует о занятости устройства. Не получив бита подтверждения, ведущее устройство должно сформировать условие Stop, чтобы освободить шину. Когда ведущее устройство является приемником, оно должно формировать нулевой бит АС К после каждого принятого байта, кроме последнего. Единичный бит АСК в этом случае является указанием ведомому

424__________ Глава 11. Вспомогательные последовательные интерфейсы и шины

устройству на окончание передачи — оно теперь должно освободить линии SDA и SCL, чтобы ведущее устройство смогло сформировать условие Р или S r.

На вышеописанной физической основе строится протокол обмена данными по PC. Каждое ведомое устройство имеет свой адрес, уникальный на шине. В начале любой передачи ведущее устройство после условия S или S г посылает адрес ведомого устройства или специальный адрес (табл. 11.1). Ведомое устройство, опознавшее свой адрес после условия Start, становится выбранным; оно обязано ответить подтверждением на адрес и последующие сигналы со стороны ведущего устройства, до получения условия Р или 5г.

В первоначальном варианте интер фейса разрядность адреса устройства составляла 7 бит, впоследствии был введен и режим 10-битной адресации, совместимый с 7-битной. На одной шине могут присутствовать устройства и с 7-битной, и 10-битной адресацией.

При 7-битной адресации в первом байте после S (Sr) ведущее устройство передает 7 бит адреса (А[6:0] в битах [7:1]) и признак операции RW (в бите О RW=1 — чтение, RW=0 — запись). Адреса ведомых устройств не должны попадать в области, указанные в таблице. Диапазоны адресов устройств различных типов централизованно выдаются изготовителям микросхем фирмой Philips. Для микросхем памяти, например, 7-битный адрес содержит две части: старшие 4 бита А[б:3] несут информацию о типе устройства (EEPROM — 1010), а младшие 3 бита А[0:2] определяют номер устройства данного типа на шине. Микросхемы с интерфейсом PC имеют три адресных входа, коммутацией которых на логические уровни 1 и 0 задается номер устройства, на который оно «отзовется», а тип устройства «зашит» в нем самом его изготовителем.

Когда ведущее устройство является передатчиком данных, оно в первом байте передает адрес ведомого устройства, при этом RW=0. Выбранное ведомое устройство отзывается подтверждением (АСК=0), после чего ведущее устройство посылает один или несколько байт данных, на каждый из которых ведомое устройство должно отвечать подтверждением.

Когда ведущее устройство является приемником данных, оно в первом байте передает адрес ведомого устройства с RW=1. Выбранное ведомое устройство также отзывается подтверждением (АСКНЗ), после чего происходит смена направления передачи и данные уже передает ведомое устройство. Ведущее устройство подтверждает каждый принятый байт, кроме последнего.

Эти передачи могут завершаться условием Р, вводимым ведущим устройством, после которого шину может захватить любое ведущее устройство. Возможны и комбинированные передачи, когда ведущее устройство после окончания очередного обмена не отдает шину, а формирует повторный старт (Sr), после чего обращается к тому же или иному устройству.

Отметим, что спецификация PC не оговаривает правил модификации внутреннего (для микросхемы) адреса данных при последовательных обращениях — их определяет разработчик устройства в соответствии с его функциями. Для памяти естественен автоинкремент адреса, упрощающий последовательные обращения. Для регистроориентированных устройств автоинкремент обычно не нужен.

11.1. Последовательные шины на базе I2C

425

|

0000000 |

0 |

|

0000 000 |

1 |

|

0000 001 |

X |

|

0000 010 |

X |

|

0000 011 |

X |

|

0000 1ХХ |

X |

|

1111 1ХХ |

X |

|

1111 ОХХ |

X |

Start — начало активного обмена

Адрес устройства шины CBUS (для совместимости)

Адрес для устройств иных шин

Зарезервировано

Код ведущего устройства режима Hs

Зарезервировано

Признак 10-битной адресации

¦ Общий вызов является широковещательным, на него должны отвечать лишь

устройства, поддерживающие соответствующие функции (см. ниже).

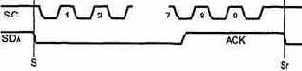

¦ Байт Start предназначен для облегчения программной реализации протокола

PC (для функций ведомых устройств, не имеющих полной аппаратной реали

зации протокола). На байт S t a r t не должно отвечать ни одно устройство. Формируемый сигнал SDA (рис. 11.2) может быть использован как запрос аппаратного прерывания, по которому процессор «вплотную» займется обработкой сигналов PC. До получения этого байта процессор (микроконтроллер) может не отвлекаться на слежение за сигналами интерфейса.

¦ На адреса шины CBUS (трехпроводный «родственник» шины PC) и иных шин

устройства PC отвечать не должны.

¦ При использовании 10-битной адресации биты [2:1] содержат старшую часть

адреса, форматы 10-адресных посылок рассмотрены ниже.

Рис. 11.2. Временная диаграмма байта Start

Посылка общего вызова используется для одной из двух целей, определяемых вторым байтом, младший бит которого называется В. При В=0 устройства, принявшие общий вызов, должны считать программируемую часть своего аппаратного адреса, выполнив (второй байт 00000110Ь) или не выполнив (ОООООЮОЬ) внутреннюю процедуру сброса. Другие значения байта устройства должны игнорировать. Каким образом программируется адрес, зависит от устройства (указывается в его описании). При В=1 общий вызов используется для широковещательной передачи данных. В этом случае ведущее устройство в старших 7 битах второго байта сообщает свой адрес (тот же, на который оно отзывается в роли ведомого), а далее

426__________ Глава 11. Вспомогательные последовательные интерфейсы и шины

посылает требуемое количество байт данных, которые оно желает донести до неизвестного ему приемника. Приемник (как правило, это интеллектуальное устройство) должен отвечать подтверждением на каждый принятый байт начиная с первого (общий вызов), затем на адрес ведущего устройства и последующие байты данных.

Широковещательная передача может использоваться, например, аппаратным контроллером клавиатуры, не знающим, на какой адрес посылать свои асинхронно возникающие сообщения. Вместо этого возможна и иная схема: по включении (и сбросу) это устройство становится ведомым приемником, которому ведущее устройство (системный контроллер) сообщит адрес потребителя информации для дальнейших «узконаправленных» передач, в которых это устройство будет уже ведущим.

Введение 10-битной адресации стало решением проблемы дефицита адресов: при 7-битной адресации с учетом зарезервированных комбинаций остается только 112 адресов, при 10-битной доступны еще 1024 адреса. Передача данных ведущим устройством с 10-битной адресацией выглядит просто: в первом байте после S (S г) биты 2:1 несут старшие биты адреса, бит 0 — признак RW=0; второй байт несет младшие 8 бит адреса, а последующие байты — передаваемые данные.

Приемник дает подтверждения обычным способом. Прием данных ведущим устройством несколько сложнее, поскольку признак RW является явным указателем на смену направления передачи и младшую часть адреса ведущее устройство передать уже не может. Прием по 10-битному адресу ведущее устройство начинает как фиктивную передачу: в первом байте посылает признак 10-битной записи и 2 бита адреса, во втором байте — остаток адреса. Далее ведущее устройство выполняет условие Sr и посылает признак 10-битного чтения (RW=1) с двумя старшими битами того же адреса. Ведомый передатчик, получив те же 2 старшие бита адреса, что и до 5г, отвечает подтверждением и начинает передавать данные ведущему устройству. Этот процесс продолжается и завершается так же, как и с 7-битной адресацией. Возможны и комбинированные обмены: реальная передача ведущего устройства 10-битному устройству, за которой после Sr следует чтение того же устройства. Также возможно комбинирование (через 5г) 7- и 10-битных обращений к разным устройствам. Широковещание с 10-битной адресацией выглядит так же, как и с 7-битной, но адрес ведущего устройства передается уже двумя байтами (младшие 8 бит адреса передаются на месте первого байта данных). Высокоскоростной режим (Hs) позволяет обмениваться данными со скоростью до 3,4 Мбит/с, причем обеспечивается обратная совместимость устройств Hs с быстрыми и стандартными (-F/5). Для обеспечения возможности обмена на столь высокой скорости выходные и входные буферы микросхем должны переключаться в специальный режим работы, отличающийся параметрами формируемых и принимаемых импульсов. Сигналы высокоскоростных устройств обозначаются как SDAH и SCLH; в смешанных системах для работы в Hs они должны отделяться от линий SDA и SCL обычных устройств специальными мостами (поведение устройств F/S на таких частотах непредсказуемо). В режиме Hs уже нет речи о разрешении конфликтов — арбитраж выполняется на скоростях F/S; также здесь нет

11.1. Последовательные шины на базе I2C_______________________________ 427

возможности синхронизации по каждому биту (замедления передачи ведомым устройством), а ведущим устройством устанавливаются жесткие соотношения длительности.низкого и высокого уровней сигнала SCLH (2:1). Ведомое устройство может притормаживать обмен только после выдачи бит подтверждений. Для перехода в режим Hs ведущее устройство в первом байте (после 5) использует зарезервированное значение 0000 1ххх, в котором ххх несет код ведущего устройства. Во время передачи этого байта (на скорости F/S) выполняется арбитраж — если обмен одновременно пытаются начать несколько устройств, продолжать его может только выигравшее ведущее устройство. Код ведущего устройства в режиме Hs назначается при конфигурировании, а все ведущие устройства на шине в режиме Hs должны иметь различные коды (код 000 зарезервирован), чем и обеспечивается завершение арбитража за время передачи первого байта. Ведущее устройство может переключиться в режим Hs, только если оно выиграло арбитраж и получило единичный бит подтверждения. В этом случае он перестраивает свои выходные и входные буферы на параметры Hs и формирует повторный старт (S г). Далее обмен логически выполняется точно так же, как и в режиме F/S, но уже на высокой скорости. Режим Hs может распространяться на несколько последующих передач, разделенных условиями S r, и завершится работа в режиме Hs по условию Р, по которому буферные схемы снова вернутся к параметрам F/S.