Режим ЕСР

Протокол ЕСР (Extended Capability Port — порт с расширенными возможностями) был предложен Hewlett Packard и Microsoft для связи с ПУ типа принтеров или сканеров. Как и ЕРР, данный протокол обеспечивает высокопроизводительный двунаправленный обмен данными хоста с ПУ. Протокол ЕСР в обоих направлениях обеспечивает два типа циклов:

¦ циклы записи и чтения данных;

¦ командные циклы записи и чтения.

Командные циклы подразделяются на два типа: передача канальных адресов и передача счетчика RLC (Run-Length Count).

30

Глава 1. Параллельный интерфейс — LPT-порт

В отличие от ЕРР вместе с протоколом ЕСР сразу появился стандарт на программную (регистровую) модель его адаптера, изложенный в документе «The IEEE 1284 Extended Capabilities Port Protocol and ISA Interface Standard» компании Microsoft. Этот документ определяет свойства протокола, не заданные стандартом IEEE 1284:

¦ компрессия данных хост-адаптером по методу RLE;

¦ буферизация FIFO для прямого и обратного каналов;

¦ применение DMA и программного ввода-вывода.

Компрессия в реальном времени по методу RLE (Run-Length Encoding) позволяет достичь коэффициента сжатия 64:1 при передаче растровых изображений, которые имеют длинные строки повторяющихся байт. Компрессию можно использовать, только если ее поддерживают и хост, и ПУ.

Канальная адресация ЕСР применяется для адресации множества логических устройств, входящих в одно физическое. Например, в комбинированном устройстве факс/принтер/модем, подключаемом только к одному параллельному порту, возможен одновременный прием факса и печать на принтере. В режиме SPP, если принтер установит сигнал занятости, канал будет занят данными, пока принтер их не примет. В режиме ЕСР программный драйвер просто адресуется к другому логическому каналу того же порта.

Протокол ЕСР переопределяет сигналы SPP (табл. 1.6). Таблица 1.6. Сигналы LPT-порта в режиме ввода-вывода ЕСР

|

||

|

|

Контакт Сигнал SPP Имя в ЕСР |

|

HostClk HostAck |

|

Strobe# AutoLF* |

|

1 14 |

О Указывает тип цикла (команда/данные) при передаче в прямом направлении. Используется как сигнал подтверждения в паре с PeriphClk для передачи в обратном направлении

|

17 |

Selectln* |

1284Active |

0 |

|

16 |

lnit# |

ReverseRequest# |

0 |

|

10 |

Ack# |

PeriphClk |

I |

|

11 |

Busy |

PeriphAck |

I |

|

12 |

PaperEnd |

AckReverse* |

I |

|

13 |

Select |

Xflag1 |

I |

в режиме IEEE 1284 (в режиме SPP уровень

низкий)

Запрос реверса. Низкий уровень сигнализирует о переключении канала на передачу в обратном направлении

Строб данных, используется в паре с HostAck для передачи в обратном направлении

Используется как сигнал подтверждения в паре с HostClk для передачи в прямом направлении. Индицирует тип команда/ данные при передаче в обратном направлении

Подтверждение реверса. Переводится

в низкий уровень в ответ на ReverseRequest*

Флаг расширяемости

1.3. Стандарт IEEE 1284

Контакт Сигнал SPP Имя в ЕСР I/O Описание

на доступность (наличие) обратного канала передачи1

2-9 Data [0:7] Data [0:7] I/O Двунаправленный канал данных

Адаптер ЕСР тоже генерирует внешние протокольные сигналы квитирования аппаратно, но его работа существенно отличается от режима ЕРР.

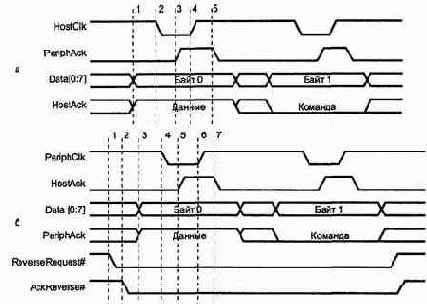

На рис. 1.5, а приведена диаграмма двух циклов прямой передачи: за циклом данных следует командный цикл. Тип цикла задается уровнем на линии HostAck: в цикле данных — высокий, в командном цикле — низкий. В командном цикле байт может содержать канальный адрес или счетчик RLE. Отличительным признаком является бит 7 (старший): если он нулевой, то биты 0-6 содержат счетчик RLE (0-127), если единичный — то канальный адрес.

На рис. 1.5, б показана пара циклов обратной передачи.

В отличие от диаграмм обмена ЕРР, на рис. 1.5 не приведены сигналы циклов системной шины процессора. В данном режиме обмен программы с ПУ разбивается на два относительно независимых процесса, которые связаны через FIFO-буфер. Обмен драйвера с FIFO-буфером может осуществляться как с использованием DMA, так и программного ввода-вывода. Обмен ПУ с буфером аппаратно выполняет адаптер ЕСР. Драйвер в режиме ЕСР не имеет информации о точном состоянии процесса обмена, но обычно важно только то, завершен он или нет.

Прямая передача данных на внешнем интерфейсе состоит из следующих шагов:

1. Хост помещает данные на шину канала и устанавливает признак цикла дан

ных (высокий уровень) или команды (низкий уровень) на линии HostAck.

2. Хост устанавливает низкий уровень на линии HostClk, указывая на действи

тельность данных.

3. ПУ отвечает установкой высокого уровня на линии PeriphAck.

4. Хост устанавливает высокий уровень линии HostClk, и этот перепад может использоваться для фиксации данных в ПУ.

5. ПУ устанавливает низкий уровень на линии PeriphAck для указания на готовность к приему следующего байта.

Поскольку передача в ЕСР происходит через FIFO-буферы, которые могут присутствовать на обеих сторонах интерфейса, важно понимать, на каком этапе данные можно считать переданными. Данные считаются переданными на шаге 4, когда линия HostClk переходит в высокий уровень. В этот момент модифицируются счетчики переданных и принятых байт. В протоколе ЕСР есть условия, вызывающие прекращение обмена между шагами 3 и 4. Тогда эти данные не должны рассматриваться как переданные.

32

Глава 1. Параллельный интерфейс — LPT-nopr

Рис. 1.5. Передача в режиме ЕСР: а — прямая, б — обратная

Из рис. 1.5 видно и другое отличие ЕСР от ЕРР. Протокол ЕРР позволяет драйверу чередовать циклы прямой и обратной передачи, не запрашивая подтверждения на смену направления.

В ЕСР смена направления должна быть согласована: хост запрашивает реверс установкой ReverseRequest*, после чего он должен дождаться подтверждения сигналом AckReverse*. Поскольку предыдущий цикл мог выполняться по прямому доступу, драйвер должен дождаться завершения прямого доступа или прервать его, выгрузить буфер FIFO, определив точное значение счетчика переданных байт, и только после этого запрашивать реверс.

Обратная передача данных состоит из следующих шагов:

1. Хост запрашивает изменение направления канала, устанавливая низкий уро

вень на линии ReverseRequest*.

2. ПУ разрешает смену направления установкой низкого уровня на линии

AckReverse*.

3. ПУ помещает данные на шину канала и устанавливает признак цикла данных

(высокий уровень) или команды (низкий уровень) на линии PeriphAck.

4. ПУ устанавливает низкий уровень на линии PeriphClk, указывая на действи

тельность данных.

5. Хост отвечает установкой высокого уровня на линии HostAck.

1.3. Стандарт IEEE 1284_______________________________________________ 33

6. ПУ устанавливает высокий уровень линии PeriphClk; этот перепад может использоваться для фиксации данных хостом.

7. Хост устанавливает низкий уровень на линии HostAck для указания на готовность к приему следующего байта.