Протокол шины PCI

В каждой транзакции (обмене по шине) участвуют два устройства — инициатор (initiator) обмена, он же ведущее (master) устройство, и целевое (target) устройство (ЦУ), оно же ведомое (slave). Шина PCI все транзакции трактует как пакетные: каждая транзакция начинается фазой адреса, за которой может следовать одна или несколько фаз данных. Состав и назначение интерфейсных сигналов шины приведены в табл. 6.11.

| Глава 6. | Шины и карты расширения | |||||||

| Таблица 6. | 11. | Сигналы шины PCI | |||||||

| Сигнал | Назначение |

AD[31:0] Address/Data — мультиплексированная шина адреса/данных. В начале транзакции передается адрес, в последующих тактах —данные

С/ВЕ[3:0]# Command/Byte Enable — команда/разрешение обращения к байтам. Команда, определяющая тип очередного цикла шины, задается четырехбитным кодом в фазе адреса „

FRAME* Кадр. Введением сигнала отмечается начало транзакции (фаза адреса), снятие сигнала указывает на то, что последующий цикл передачи данных является последним в транзакции

DEVSEL* Device Select — устройство выбрано (ответ ЦУ на адресованную к нему транзакцию)

IRDY* Initiator Ready — готовность ведущего устройства к обмену данными

TRDY* Target Ready — готовность ЦУ к обмену данными

STOP* Запрос ЦУ к ведущему устройству на остановку текущей транзакции

LOCK* Сигнал захвата шины для обеспечения целостного выполнения операции. Используется мостом, которому для выполнения одной операции требуется выполнить несколько транзакций PCI

REQ# Request — запрос от ведущего устройства на захват шины

GNT# Grant — предоставление ведущему устройству управления шиной

PAR Parity — общий бит паритета для линий AD[31:0] и С/ВЕ[3:0]#

PERR* Parity Error — сигнал об ошибке паритета (для всех циклов, кроме специальных). Вырабатывается любым устройством, обнаружившим ошибку

РМЕ# Power Management Event — сигнал о событиях, вызывающих изменение режима

потребления (дополнительный сигнал, введенный в PCI 2.2)

CLKRUN* Clock running — шина работает на номинальной частоте синхронизации. Снятие сигнала означает замедление или остановку синхронизации с целью снижения потребления (для мобильных применений)

PRSNT[1,2]# Present — индикаторы присутствия платы, кодирующие запрос потребляемой мощности. На карте расширения одна или две линии индикаторов соединяются с шиной GND, что воспринимается системной платой

RST# Reset — сброс всех регистров в начальное состояние

IDSEL Initialization Device Select — выбор устройства в циклах конфигурационного

считывания и записи

SERR# System Error — системная ошибка. Ошибка паритета адреса данных в специальном цикле или иная катастрофическая ошибка, обнаруженная устройством. Активизируется любым устройством PCI и вызывает NMI

REQ64* Request 64 bit — запрос на 64-битный обмен. Сигнал вводится 64-битным

инициатором, по времени он совпадает с сигналом FRAME*. Во время окончания сброса (сигналом RST*) сигнализирует 64-битному устройству о том, что оно подключено к 64-битной шине. Если 64-б.итное устройство не обнаружит этого сигнала, оно должно переконфигурироваться на 32-битный режим, отключив буферные схемы старших байтов

АСК64* Подтверждение 64-битного обмена. Сигнал вводится 64-битным ЦУ, опознавшим свой адрес, одновременно с DEVSEL*. Отсутствие этого подтверждения заставит инициатор выполнять обмен с 32-битной разрядностью

INTA#, INTB*, Interrupt А, В, С, D — линии запросов прерывания, чувствительность к уровню, INTC#, INTD* активный уровень — низкий, что допускает разделяемость (совместное использование)линий

CLK Clock — тактовая частота шины. Должна лежать в пределах 20—33 МГц,

вPCI2.1— до 66 МГц

M66EN 66MHz Enable — разрешение частоты синхронизации до 66 МГц

6.2. Шина PCI 179

SBO# Snoop Backoff — попадание текущего обращения к памяти абонента шины

в модифицированную строку кэша. Необязательный сигнал, используется только абонентами шины с кэшируемой памятью при алгоритме обратной записи

ТСК Test Clock — синхронизация тестового интерфейса JTAG

TDI Test Data Input — входные данные тестового интерфейса JTAG

TOO Test Data Output — выходные данные тестового интерфейса JTAG

TMS Test Mode Select — выбор режима для тестового интерфейса JTAG

TRST Test Logic Reset — сброс тестовой логики

Для адреса и данных используются общие мультиплексированные линии AD. Четыре мультиплексированные линии С/ВЕ[3:0] обеспечивают кодирование команд в фазе адреса и разрешения байт в фазе данных. В начале транзакции ведущее устройство активизирует сигнал FRAME*, по шине AD передает целевой адрес, а по линиям С/ВЕ# — информацию о типе транзакции (команде).

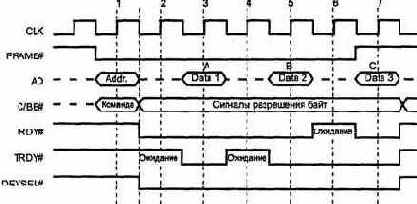

Адресованное ЦУ отзывается сигналом DEVSEL*. Ведущее устройство указывает на свою готовность к обмену данными сигналом IRDY#, эта готовность может быть выставлена и раньше получения DEVSEL*. Когда к обмену данными будет готово и ЦУ, оно установит сигнал TRDY*. Данные по шине AD передаются только при одновременном наличии сигналов IRDY# и TRDY*. С помощью этих сигналов ведущее устройство и ЦУ согласуют свои скорости, вводя такты ожидания. На рис. 6.7 приведена временная диаграмма обмена, в которой и ведущее устройство, и ЦУ вводят такты ожидания. Если бы они оба ввели сигналы готовности в конце фазы адреса и не снимали их до конца обмена, то в каждом такте после фазы адреса передавались бы по 32 бита данных, что обеспечило бы выход на предельную производительность обмена.

Количество фаз данных в пакете явно не указывается, но перед последней фазой данных ведущее устройство при введенном сигнале IRDY* снимает сигнал FRAME*. В одиночных транзакциях сигнал FRAME* активен лишь один такт. Если устройство не поддерживает пакетные транзакции в ведомом режиме, то оно должно потребовать прекращения пакетной транзакции во время первой фазы данных (введя сигнал STOP* одновременно с TRDY*). В ответ на это ведущее устройство завершит данную транзакцию и продолжит обмен последующей транзакцией с новым

180

Глава 6. Шины и карты расширения

Рис. 6.7. Цикл обмена на шине PCI

Шина позволяет уменьшить мощность (ток), потребляемую устройствами, ценой снижения производительности, применяя пошаговое переключение линий AD[31:0] и PAR (address/data stepping). Здесь возможны два варианта.

¦ Плавный шаг (continuous stepping) — начало формирования сигналов слабо

точными формирователями за несколько тактов до введения сигнала-квалифи-

катора действительной информации (FRAME# в фазе адреса, IRDY# или TRDY# в фазе данных). За эти несколько тактов сигналы «доползут» до требуемого значения при меньшем токе.

¦ Дискретный шаг (diskrete stepping) — нормальные формирователи срабатывают не все сразу, а группами (например, побайтно), в каждом такте по группе. При этом снижаются броски тока, поскольку одновременно переключается меньше формирователей.

Устройство само может и не пользоваться этими возможностями (см. бит 7 регистра команд), но должно «понимать» такие циклы. Задерживая сигнал FRAME*, устройство рискует потерять право доступа к шине, если арбитр получит запрос от более приоритетного устройства.

6.2. Шина PCI______________________________________________________ 181

Протокол квитирования обеспечивает надежность обмена — ведущее устройство всегда получает информацию об отработке транзакции ЦУ. Средством повышения надежности (достоверности) является применение контроля паритета: линии AD[31:0] и С/ВЕ[3:0]# и в фазе адреса, и в фазе данных защищены битом паритета PAR (количество единичных бит этих линий, включая PAR, должно быть четным). Действительное значение PAR появляется на шине с задержкой в один такт относительно линий AD и С/ВЕ#. При обнаружении ошибки ЦУ вырабатывается сигнал PERR* (со сдвигом на такт после действительности бита паритета). В подсчете паритета при передаче данных учитываются все байты, включая и недействительные (отмеченные высоким уровнем сигнала С/ВЕх#). Состояние бит, даже и в недействительных байтах данных, во время фазы данных должно оставаться стабильным.

Каждая транзакция на шине должна быть завершена планово или прекращена, при этом шина должна перейти в состояние покоя (сигналы FRAME* и IRDY# пассивны). Завершение транзакции выполняется либо по инициативе ведущего устройства, либо по инициативе ПУ. Ведущее устройство может завершить транзакцию одним из следующих способов.

¦ Нормальное завершение ( Camletiori) выполняется по окончании обмена данными.

¦ Завершение по тайм-ауту (Time-out) происходит, когда во время транзакции у ведущего устройства отбирают право на управление шиной (снятием сигнала GNT#) и истекает время, указанное в его таймере Latency Timer. Это может случиться, если адресованное ЦУ оказалось непредвиденно медленным или запланирована слишком длинная транзакция. Короткие транзакции (с одной - двумя фазами данных) даже в случае снятия сигнала GNT# и срабатывания таймера завершаются нормально. Транзакция отвергается (Master-Abort), когда в течение заданного времени ведущее устройство не получает ответа ЦУ (DEVSEL*).

Транзакция может быть прекращена по инициативе ЦУ; для этого оно может ввести сигнал STOP*. Возможны три типа прекращения.

¦ Повтор (Retry) — сигнал STOP* вводится при пассивном сигнале TRDY* до первой фазы данных. Эта ситуация возникает, когда ЦУ из-за внутренней занятости не успевает выдать первые данные в положенный срок (16 тактов). Повтор является указанием ведущему устройству на необходимость нового запуска той же транзакции.

¦ Отключение (Disconnect) — сигнал STOP* вводится во время или после первой фазы данных. Если сигнал STOP* введен при активном сигнале TRDY* очередной фазы данных, то эти данные передаются и на том транзакция завершается. Если сигнал STOP* введен при пассивном сигнале TRDY*, то транзакция завершается без передачи данных очередной фазы. Отключение производится, когда ЦУ неспособно своевременно выдать или принять очередную порцию данных пакета.

¦ Отказ (Target-Abort) — сигнал STOP* вводится одновременно со снятием сигнала DEVSEL* (в предыдущих случаях во время появление сигнала STOP* сигнал DEVSEL* был активен). После этого данные уже не передаются. Отказ вводится, когда ЦУ обнаруживает фатальную ошибку или иные условия, по которым оно уже никак не сможет обслужить данный запрос.

182-:________________________________________________________________ Глава 6. Шины и карты расширения

Использование трех типов прекращения вовсе не обязательно для всех ЦУ, однако любое ведущее устройство должно быть готово к завершению транзакций по любой из этих причин.