Параллельный интерфейс АТА

Параллельный интерфейс АТА представляет собой шину, в которой все сигналы соответствуют стандартной логике ТТЛ:

¦ высокий уровень выходного сигнала не ниже 2,4 В (при токе до 400 мкА, сигнал DMARQ — до 500 мкА), низкий уровень не выше 0,5 В (при токе 4 мА, для линии DASP ради совместимости со старыми устройствами — 12 мА);

¦ высокий уровень входного сигнала не ниже 2,0 В, низкий уровень не выше 0,8 В.

Все информационные сигналы интерфейса передаются через 40-контактный разъем, у которого ключом является отсутствующий на вилке и закрытый на розетке контакт 20. Использование в качестве ключа выступа на корпусе розетки и прорези в бандаже вилки стандартом не приветствуется. Для соединения устройств применяется плоский многожильный кабель-шлейф, длина кабеля не должна превышать 0,46 м(18"), допустимая емкость проводников — неболее 35 пФ. Терминаторы стандартом не предусматриваются (они имеются в каждом устройстве и хост-адаптере), но если кабель с тремя разъемами (розетками) используют для подключения одного устройства, то устройство и хост-адаптер рекомендуется подключать к противоположным концам кабеля. Состав информационных сигна-

9.2. Интерфейс ATA/ATAPI (IDE)

363

Таблица 9.3. Интерфейс ATA (IDE)

| Сигнал | Тип1 | Контакт | Контакт | Тип1 | Сигнал | ||||||

| reSet# | 1 | 1 | 2 | - | GND | ||||||

| DD7 | I/OTS | 3 | 4 | I/OTS | DD8 | ||||||

| DD6 | I/OTS | 5 | 6 | I/OTS | DD9 | ||||||

| DD5 | I/OTS | 7 | 8 | I/O TS | DD10 | ||||||

| DD4 | I/OTS | 9 | 10 | I/OTS | DD11 | ||||||

| DD3 | I/OTS | 11 | 12 | I/O TS | DD12 | ||||||

| DD2 | I/OTS | 13 | 14 | I/OTS | DD13 | ||||||

| DD1 | I/OTS | 15 | 16 | I/OTS | DD14 | ||||||

| DDO | I/OTS | 17 | 18 | I/OTS | DD15 | ||||||

| GND | - | 19 | 20 | - | Ключ (нет штырька) | ||||||

| DMARQ | OTS2 | 21 | 22 | - | GND | ||||||

| DlOWtf/STOP3 | 1 | 23 | 24 | - | GND | ||||||

| DIOR#/HDMARDY#/HSTROBE3 | 1 | 25 | 26 | - | GND | ||||||

| IORDY/DDMARDY#/DSTROBE3 | OTS2 | 27 | 28 | I/O | SPSYNC/CSEL7 | ||||||

| DMACK# | 1 | 29 | 30 | - | GND | ||||||

| INTRQ | OTS2 | 31 | 32 | ОOK | IOCS16#8 | ||||||

| DA1 | 1 | 33 | 34 | I,O> | PDIAG#/CBLID3 | ||||||

| DAO | 1 | 35 | 36 | 1 | DA2 | ||||||

| CSO# | 1 | 37 | 38 | 1 | CS1# | ||||||

| DASP# | I/O OK5 | 39 | 40 | - | GND | ||||||

| +5 В (Logic) | - | 41е | 426 | - | +5 В (Motor) | ||||||

| GND | - | 436 | 446 | - | Зарезервирован |

1 Тип сигнала для устройства: I — вход, О— выход, I/O — двунаправленный, TS — тристабильный, ОК —

открытый коллектор. Для хост-адаптера значения I и О имеют противоположный смысл.

2 У старых устройств сигнал может иметь тип ОК (при разнотипных сигналах на одной шине возможен

конфликт).

3 Сигналы, приведенные после символа /,используются только в режиме Ultra DMA (AT A-4).

4 У ведущего устройства —' вход, у ведомого — выход.

5 У ведомого устройства — только выход.

6 Контакты 41-44 используются только для миниатюрных дисков.

7 Начиная с АТА-3 - только CSEL.

8 Начиная с АТ А-3 зарезервирован.

364

Глава 9. Интерфейсы устройств хранения

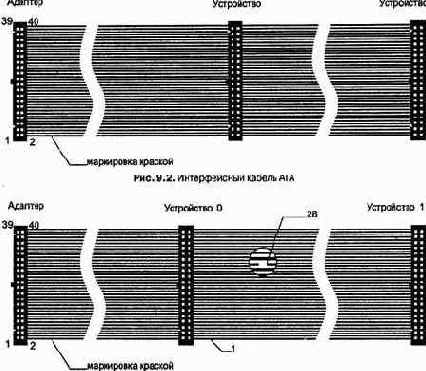

Рис. 9.3. Ленточный кабель интерфейса АТА с кабельной выборкой

Начиная с ATA/ATAPI-4 в шлейфах узаконили кабельную выборку и для подключения устройства 1 определили средний коннектор. В нем контакт 28 либо не соединен с проводом, либо просто отсутствует. Вполне понятно, что при использовании кабельной выборки хост-контроллер подключать к среднему коннектору нельзя (как и к правому на рис. 9.3). Если номер устройства назначается джампером, то для 40-проводного кабеля можно подключать устройства и хост-контроллер к любым коннекторам произвольно (но желательно избегать «висячих» концов).

Для устойчивой работы в режиме Ultra DMA рекомендуется применение 80-про-водных кабелей, обеспечивающих чередование сигнальных цепей и проводов схемной земли (GND). Такие кабели требуются для режимов UltraDMA выше 2 (скорость выше 33 Мбайт/с). Эти кабели разделываются на специальные разъемы, имеющие 40-контактные гнезда с обычным назначением контактов, но ножевые контакты для врезки 80 проводов. В шлейфе для схемной земли используются либо все четные, либо все нечетные провода — это зависит от применяемых разъемов (на них должна быть маркировка EVN GND или ODD GND соответственно). Установка

9.2. Интерфейс АТА/ATAPI (IDE)_______________________________________ 365

на одном шлейфе разнотипных разъемов недопустима (тогда все 80 проводов окажутся соединенными вместе).

На 80-проводном кабеле в разъеме для подключения контроллера контакт 34 соединен с шиной GND и не соединен с проводом шлейфа; этим обеспечивается идентификация типа кабеля (CBLID). Провод шлейфа соединяет контакты 34 разъемов устройств, что обеспечивает прохождение сигнала PDIAG* от ведомого устройства к ведущему. С учетом возможности кабельной выборки на 80-проводном шлейфе положение коннекторов уже однозначно.

¦ Коннектор хост-контроллера расположен на конце шлейфа, у него контакт 34 заземлен и не соединен со шлейфом. Корпус коннектора должен быть синего цвета .

¦ Коннектор устройства 0 расположен на противоположном конце шлейфа, у

него все контакты соединены со шлейфом. Корпус коннектора должен быть

черного цвета.

¦ Коннектор устройства 1 (необязательный) расположен в середине шлейфа, у него контакт 28 не соединен со шлейфом. Корпус коннектора должен быть серого цвета.

Если кабельная выборка не используется, то устройства 0 и 1 можно менять местами.

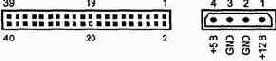

Спецификация АТА «узаконивает» как 40-контактный интерфейсный разъем, так и 4-контактный разъем питания (рис. 9.4), но для малогабаритных устройств питание может подаваться по 44-проводному интерфейсному кабелю.

А б

Рис. 9.4. Разъемы интерфейса АТА (вилки на устройствах): а — интерфейсный, б — питания

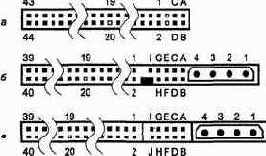

Для большинства устройств применяется 40-контактный разъем с шагом контактов 2,54 мм. Рядом с ним могут располагаться дополнительные контакты, служащие для конфигурирования устройства и технологических целей (диагностики и других операций по служебному последовательному интерфейсу). Спецификация AT A/ AT API предусматривает два варианта, приведенные на рис. 9.5, а и б. Здесь пустым квадратиком обозначены позиции ключевых (пропущенных) выводов, контакты 1-40 используются для интерфейса (см. табл. 9.3), а контакты А-Н — для установки джамперов (табл. 9.4) и технологических целей.

Для миниатюрных устройств предназначен 50-контактный разъем с шагом выводов 2 мм (рис. 9.5, в), у которого контакты 1-44 соответствуют табл. 9.3, контакты A-D — табл. 9.4 (используются для конфигурирования, а пара пропущенных контактов является дополнительным ключом). Для 50-контактного кабеля принято назначение выводов накопителей IBM Thinkpad/Travelstar:

¦ контакт А через резистор 10 кОм соединяется с шиной +5 В;

¦ контакт В для устройства задает его роль: низкий уровень — устройство 0, высокий — устройство 1;

366________________________________ Глава 9. Интерфейсы устройств хранения

¦ контакт С определяет режим устройства по включении питания: низкий уро

вень — Standby, высокий — Idle;

¦ контакт D соединяется с контактом 28 (CSEL) и через резистор 10 кОм — с шиной +5 В.

Это назначение, позволяющее конфигурировать и адресацию, и режим потребления, применяется не на всех устройствах. На винчестерах фирмы Toshiba контакты А и В могут использоваться как выход и вход последовательного интерфейса (В подтянут к шине +5 В через резистор 47 кОм), С — GND, D — роль устройства (низкий уровень для устройства 1).

Рис. 9.5. Дополнительные контакты на разъемах интерфейса АТА: а — SFF8057, б — SFF8058, в — SFF8212 (50-контактный разъем)

Таблица 9.4. Использование дополнительных контактов

|

Выборка |

SFF8057 |

SFF8058 |

SFF8212 |

Toshiba (1996) |

|

Используемые контакты |

Е-Н |

A-F |

A-D |

A-D |

|

Кабельная выборка |

E-F |

A-B |

B-D |

B-D |

|

Master |

G-H |

E-F |

- |

- |

|

Master при наличии Slave |

G-H,E-F |

E-F |

- |

- |

|

Slave |

- |

C-D |

A-B |

C-D |

В документации на устройства могут быть указаны несколько отличающиеся обозначения сигналов.

Здесь приведены обозначения из стандарта ATA/ATAPI-4.

¦ RESET* (Device Reset) — сброс устройства (инвертированный сигнал сброса системной шины). Сигнал длительностью не менее 25 мкс вырабатывается после установления питающих напряжений. Сигнал вызывает сброс интерфейса в исходное состояние и устанавливает параметры по умолчанию.

Э.2. Интерфейс АТА/ATAPI (IDE) ___________________________________ 367

¦ DA[2:0] (Device Address) — три младших бита системной шины адреса, используемые для выбора регистров устройств.

¦ DD[15:0] (Device Data) — двунаправленная 16-битная шина данных между адаптером и устройствами. При 8-битных обменах используются младшие биты D[7:0]. У устройства не должно быть «подтягивающего» резистора на линии DD7 — на хост-контроллере эта линия через резистор 10 кОм соединена с шиной GND. Это позволяет хосту определить факт отсутствия устройства на шине сразу после аппаратного сброса: при чтении регистра состояния отсутствующего устройства бит BSY окажется сброшенным.

¦ DIOR* (Device I/O Read) — строб чтения портов ввода-вывода. Данные фиксируются по положительному перепаду сигнала.

¦ DIOW# (Device I/O Write) — строб записи портов ввода-вывода. Данные фиксируются по положительному перепаду сигнала.

¦ IORDY (I/O channel Ready) — готовность устройства завершить цикл обмена. Низким уровнем сигнала во время цикла обмена устройство может ввести такты ожидания шины. Сигнал требуется при обмене в РЮ Mode 3 и выше. На хост-контроллере эта линия через резистор 1 кОм должна подтягиваться к шине питания.

¦ IOCS16* — разрешение 16-битных операций. Обращение ко всем регистрам, кроме регистра данных, всегда 8-битное. Для РЮ Mode 0,1,2 при активном сигнале обращения 16-битные, при неактивном — 8-битные. Для РЮ Mode 3,4 и DMA все обмены 16-битные, кроме дополнительных байтов (выходящих за границу 512-байтного сектора) «длинного» считывания и записи.

Начиная с ATA/ATAPI-3 не используется.

¦ DMARQ (DMA Request) — запрос обмена по каналу DMA (необязательный). При разрешении обмена сигнал (высокий уровень) вводится устройством по готовности к обмену. Введя сигнал DMARQ, устройство должно дождаться подтверждения от хост-адаптера сигналом DMACK*, после чего может снять запрос DMARQ. Для очередной передачи запрос должен быть введен снова. В режиме Multiword DMA запрос может удерживаться на время передачи всех данных. Выход должен быть тристабильным, во время работы с DMA он может быть в активном состоянии (0 или 1) только у выбранного устройства. В АТА-1 для

этого сигнала мог использоваться как тристабильный, так и стандартный ТТЛ-

выход. Работа на одной шине устройств с разнотипными выходами DMARQ может привести к конфликтам. На хост-контроллере линия должна соединяться с шиной GND через резистор 5,6 кОм.

¦ DMACK# (DMA Acknowledge) — подтверждение DMA. Сигнал вырабатывается хост-адаптером как подтверждение цикла передачи. Передача слова данных управляется сигналами DIOR* или DIOW*. Во время обмена по каналу DMA сигналы IOCS16#, CSO# и CS1# не используются, обмен всегда производится 16-битными словами.

¦ INTRQ (Interrupt Request) — запрос прерывания. Выход должен быть тристабильным, активный сигнал (логическую единицу) вырабатывает только вы-

368________________________________ Глава 9. Интерфейсы устройств хранения

бранное устройство, когда у него имеется необслуженный запрос прерывания и его вырабатывание не запрещено битом n IE N в регистре Device Control.Запрос сбрасывается по сигналу RESET*, установке бита SRST в регистре Devi се Control, записи в регистр команд или чтении регистра состояния. При обменах PIO запрос устанавливается в начале передачи каждого блока (сектора или группы секторов при многосекторных операциях). Исключения: по командам Format Track, Write Sector(S),Write Buffer и Write Long в начале передачи первого блока данных запрос прерывания не вырабатывается.

При обме нах DMA запрос прерывания вырабатывается только по завершении операции. На хост-контроллере эта линия через резистор 10 кОм должна подтягиваться к шине GND.

¦ CSO# (Chip Select 0) — сигнал выбора блока командных регистров (Command Block Registers). Для первого канала он вырабатывается при наличии на системной шине адреса порта ввода-вывода в диапазоне !FOh-lF7h (сигнал так же называют CS1FX*).

¦ CS1# (Chip Select 1) — выбор блока управляющих регистров (Control Block

Registers). Для первого канала он вырабатывается при наличии на системной шине адреса порта ввода-вывода в диапазоне 3F6h-3F7h (часто этот сигнал называется CS3FX*).

¦ PDIAG* (Passed Diagnostics) — сигнал о прохождении диагностики. Ведущее устройство наблюдает за этим сигналом, который ведомое устройство должно выработать в ответ на сброс или команду диагностики. Если ведомое устройство обнаружено (по сигналу DASP#), ведущее устройство ожидает сигнал в течение 31с после сброса и 6 с после команды диагностики. Если за это время сигнал не появился, ведущее устройство отмечает этот факт установкой бита 7 регистра ошибок. Если ведомое устройство не обнаружено, ведущее обнуляет регистр состояния ведомого устройства и сообщает свое состояние сразу после завершения собственной самодиагностики. Сигнал служит только для связи двух устройств и хост-адаптером не используется (в АТА-4 контакт задействован для сигнала CBLID*).

¦ CBLID* (Cable assembly type identifier) — идентификация типа кабеля. В 80-проводной сборке контакт 34 на разъеме хост-адаптера соединяется с шиной GND, а контакты 34 разъемов устройств соединяются между собой, но связи с разъемом хост-адаптера не имеют. На устройстве эта линия через резистор 10 кОм должна подтягиваться к шине питания. После прохождения сброса (когда сигнал PDIAG* снимается) хост может определить наличие 80-проводного кабеля по низкому уровню сигнала.

¦ DASP# (Device Active, Slave Present) — сигнал двойного назначения: индикатор активности устройства и присутствия ведомого устройства. Устройства имеют выход типа «открытый коллектор» с нагрузочным резистором 10 кОм к шине +5 В. После сброса по сигналу RESET* или при инициализации по включении питания оба устройства в течение 1 мс должны деактивировать этот сигнал, после чего не позже чем через 400 мс его вводит ведомое устройство для сообщения о своем присутствии. Ведущее устройство не активирует этот сиг-

9.2. Интерфейс АТА/ATAPI (IDE) 369

нал в течение 450 мс. Сигнал деактивируется ведомым устройством после получения им команды или через 31 с автоматически (смотря что произойдет раньше). После этого сигнал может быть введен любым устройством как индикатор активности. Адаптер использует этот сигнал для включения светодиодного индикатора доступа к диску.

¦ SPSYNC/CSEL (Spindle Synchronization/Cable Select) — синхронизация шпинделя или выборка кабелем. Сигнал двойного назначения, которое должно быть единым для обоих устройств. Сигнал SPSYNC позволяет синхронизировать шпиндели устройств (актуально для RAID-массивов); используется по усмотрению производителя накопителя, начиная с ATA/ATAPI-3 этот сигнал из спецификации изъят. Сигнал CSEL позволяет устройствам определять свой адрес по положению на специальном кабеле с разрывом провода 28 между разъемами двух устройств (малораспространенная «кабельная выборка»). Эта линия на хост-адаптере заземлена, и ведущее устройство получает заземленную линию, а ведомое — неподключенную. На устройстве линия подтягивается к высокому уровню резистором 10 кОм. Состояние сигнала (если он управляется хост-адаптером) должно удерживаться по крайней мере 31с после сигнала RESET*.

При использовании режима Ultra DMA четыре линии получают новое назначение сигналов.

¦ STOP (Stop Ultra DMA burst) — останов передачи пакета Ultra DMA.

¦ DDMARDY* (Device Ultra DMA ready) — готовность устройства при приеме пакета Ultra DMA (управление потоком).

¦ DSTROBE ( Host Ultra DMA data strobe) — строб данных устройства при передаче пакета хосту. Данные передаются по обоим перепадам DSTROBE.

¦ HDMARDY* (Host Ultra DMA ready) — готовность хоста при приеме им пакета Ultra DMA (управление потоком).

¦ HSTROBE (Host Ultra DMA data strobe) — строб данных хоста при передаче пакета устройству. Данные передаются по обоим перепадам HSTROBE.

Для блокнотных ПК в стандарте имеется вариант интерфейса IDE на 68-контактном разъеме PCMCIA (PC Card), приведенный в табл. 9.5. Здесь имеется ряд специфичных сигналов.

¦ SELATA* (Select 68-pin ATA) — сигнал, которым хост идентифицирует режим использования разъема, PC Card (сигнал снят) или АТА (сигнал установлен, то есть низкий уровень). Этот сигнал хост должен установить до подачи питания на коннектор. В течение 19 мс после подачи питания устройство игнорирует все интерфейсные сигналы, кроме этого. Если этот сигнал активен, то устройство должно сконфигурироваться на режим АТА. Если сигнал неактивен, оно должно сконфигурироваться на режим PC Card или не отвечать на другие сигналы хоста.

¦ CD1 # и CD2# (Card Detect) заземляются в устройстве — по этим сигналам хост определяет присутствие устройства.

¦ CS1# (Device chip select 1) — выбор устройства, подается хостом на оба контакта (Ни 42), но устройство воспринимает только один из них.

370

Глава 9. Интерфейсы устройств хранения

¦ DMARQ, DMACK* и IORDY — не обязательны для использования.

¦ M/S# (Master/Slave) — инверсия сигнала CSEL. Хост выдает сигналы M/S# и CSEL до подачи питания, устройство воспринимает лишь один из них.

Для обеспечения «горячего» подключения разъем для цепи GND обеспечивает более раннее соединение при подключении и более позднее при отключении.

В устройстве сигналы CSO#, CS1#, RESET* и SELATA* подтягиваются к пассивному состоянию.

Таблица 9.5.68- контактный интерфейс АТА для PC Card (PCMCIA) Контакт Сигнал Контакт Сигнал

|

1 |

GND |

35 |

GND |

|

2 |

DD3 |

36 |

CD1# |

|

3 |

DD4 |

37 |

DD11 |

|

4 |

DD5 |

38 |

DD12 |

|

5 |

DD6 |

39 |

DD13 |

|

6 |

DD7 |

40 |

DD14 |

|

7 |

CSO# |

41 |

DD15 |

|

8 |

42 |

CS1# |

|

|

9 |

SELATA* |

43 |

|

|

10 |

44 |

DIOR# |

|

|

11 |

CS1# |

45 |

DIOW# |

|

12 |

46 |

||

|

13 |

47 |

||

|

14 |

48 |

||

|

15 |

49 |

||

|

16 |

INTRQ |

50 |

|

|

17 |

+5 В |

51 |

+5 В |

|

18 |

52 |

||

|

19 |

53 |

||

|

20 |

54 |

||

|

21 |

55 |

M/S# |

|

|

22 |

56 |

CSEL |

|

|

23 |

57 |

||

|

24 |

58 |

RESET# |

|

|

25 |

59 |

IORDY* |

|

|

26 |

60 |

DMARQ |

|

|

27 |

DA2 |

61 |

DMACK# |

|

28 |

DA1 |

62 |

DASP# |

|

29 |

DAO |

63 |

PDIAG* |

|

30 |

DDO |

64 |

DD8 |

|

31 |

DD1 |

65 |

DD9 |

|

32 |

DD2 |

66 |

DD10 |

|

33 |

67 |

CD2# |

|

|

34 |

GND |

68 |

GND |

9.2. Интерфейс АТА/ATAPI (IDE)_______________________________________ 371

Для компьютеров класса ЛТ существует 8-битная версия интерфейса, называемая XT-IDE, реже — XT-Bus. Этот интерфейс [2,5], как и AT А, реализован на 40-провод-ном кабеле, и многие его сигналы совпадают с 16-битной шиной AT А. Интерфейс XT-IDE можно рассматривать как подмножество AT А, хотя прямой совместимости нет. Ряд устройств АТА имеют джампер выбора режима XT/AT (в накопителях Seagate на это указывает окончание «АХ» в обозначении модели).

Регистры устройств

Каждое устройство АТА имеет стандартный набор регистров, адресуемых сигналами от хост-адаптера (CSO#, CS1#, DA2, DA1, ОАО, DIOR* и DIOW#). Набор регистров (табл. 9.6) состоит из двух блоков, выбираемых сигналами CSO# и CS1#, из которых активным (низкий уровень, «О») может быть только один. В таблице приведены адреса регистров в пространстве ввода-вывода IBM PC-совместимого ПК для первого и второго каналов АТА.

При обращении к регистрам сигнал DMACK* должен быть неактивным. Блок командных регистров служит для посылки команд устройству и чтения информации о его состоянии. Блок управляющих регистров используется для управления устройством и получения более подробной информации о его состоянии. На действительность содержимого регистров командного блока и альтернативного регистра состояния указывает нулевое значение бита BSY регистра состояния. Запись в регистры должна производиться лишь при BSY=0 и DRQ=0, кроме особо оговоренных случаев. Если устройство поддерживает управление энергопотреблением, в «спящем» режиме содержимое этих регистров недействительно и запись игнорируется, кроме особо оговоренных случаев.

Таблица 9.6. Регистры контроллеров устройств АТА

|

Адрес |

Сигналы адресации канала № |

Назначение (R — чтение, W — запись) |

||||

|

(0 — низкий уровень, 1 — высокий) |

||||||

|

1 |

2 |

CSO# |

CS1# |

DA2 |

DA2 DA1О |

|

|

1 |

1 |

X |

X X |

Нет обращения (шина данных в третьем |

||

|

состоянии) |

||||||

|

0 |

0 |

X |

x X |

Недопустимый адрес (шина данных в третьем |

||

|

состоянии) |

||||||

|

3FX |

37Х |

Control Block Registers — блок управляющих регистров |

||||

|

1 |

0 |

0 |

X X |

Не используется (шина данных в третьем |

||

|

состоянии) |

||||||

|

1 |

0 |

1 |

0 X |

Не используется (шина данных в третьем |

||

|

состоянии) |

||||||

|

3F6 |

376 |

1 |

0 |

1 |

1 0 |

R: Alternate Status (AS) — альтернативный |

|

регистр состояния |

||||||

|

3F6 |

376 |

1 |

0 |

1 |

1 0 |

W: Device Control (DC) — регистр управления |

|

устройством |

||||||

|

3F7 |

377 |

1 |

0 |

1 |

1 1 |

R: Drive Address (DA) — регистр адреса |

|

(не используется)1 |

372________________________________ Глава 9. Интерфейсы устройств хранения

Таблица 9.6. (продолжение)

1 2 CSO# CS1# DA2 DA1 ОАО______________________________________________

1FX 17Х Command Block Registers — блок командных регистров

|

1F0 |

170 |

0 |

1 |

0 |

0 |

0 |

|

1F1 |

171 |

0 |

1 |

0 |

0 |

1 |

|

1F1 |

171 |

0 |

1 |

0 |

0 |

1 |

|

1F2 |

172 |

0 |

1 |

0 |

1 |

0 |

|

1F3 |

173 |

0 |

1 |

0 |

1 |

1 |

|

1F4 |

174 |

0 |

1 |

1 |

0 |

0 |

|

1F5 |

175 |

0 |

1 |

1 |

0 |

1 |

|

1F6 |

176 |

0 |

1 |

1 |

1 |

0 |

|

1F7 |

177 |

0 |

1 |

1 |

1 |

1 |

|

1F7 |

177 |

0 |

1 |

1 |

1 |

1 |

R: Error (ER) — регистр ошибок

W: Features (FR) — регистр свойств

R/W: Sector Count (SC) — регистр счетчика секторов

R/W: Sector Number (SN) — регистр номера

сектора/LBA[7:0]2

R/W: Cylinder Low (CL) — регистр младшего

байта номера цилиндраДВА[15:8]2

R/W: Cylinder High (CH) — регистр старшего байта номера цилиндра/1-ВА[23:1 б]2

R/W: Device/Head (D/H) — регистр номера устройства и головки/1_ВА[27:24]2

R: Status (SR) — регистр состояния

W: Command (CR) — регистр команд

2 Регистры сектора, цилиндра и головки в режиме LBA содержат указанные биты логического адреса.

Альтернативный регистр состояния AS (для первого канала адрес 3F6h, для второго — 376h) имеет те же биты, что и основной (см. ниже), но его чтение не приводит ни к каким изменениям состояния устройства.

Регистр управления устройством DC (3F6h, 376h) служит для программного сброса обоих устройств одновременно и управления разрешением прерывания выбранного устройства. Запись в этот регистр возможна в любой момент. Программный сброс через регистр DC должен отрабатываться ив состоянии Sleep. Назначение битов регистра DC:

¦ биты [7:3] зарезервированы;

¦ бит 2 — SRST (Software Reset) — программный сброс, действует все время, пока бит не будет снят (оба устройства на шине воспринимают программный сброс одновременно);

¦ бит 1 — n IE N (Interrupt Enable) — инверсный бит разрешения прерывания (при нулевом значении бита выбранное устройство может вырабатывать сигнал INTRQ через тристабильный выход);

¦ бит 0 - 0.

Регистр адреса устройства DA (3F7h, 377h) использовался только в первой версии АТА для совместимости со старыми контроллерами, чтением этого регистра можно было определить адресованный привод и головку. Регистр выпадает из блока (он совпадает с диагностическим регистром состояния онтроллера НГМД)

9.2. Интерфейс АТА/ATAPI (IDE)_______________________________________ 373

и рекомендуется, чтобы устройство АТА не отвечало на чтение этого регистра. Если устройство отвечает на чтение, то оно не должно управлять битом DD7 во избежание конфликта с контроллером НГМД, у которого по этой линии передается бит смены носителя. Из-за несоблюдения этого требования могут возникать проблемы, когда контроллер (адаптер) АТА и контроллер НГМД находятся на разных платах. Назначение битов регистра DA:

¦ бит 7 — (HiZ) — высокоимпедансный, при считывании не выдается на шину;

¦ бит 6 — nWTG — инверсный признак записи (во время физического выполнения записи на носитель бит нулевой);

¦ биты [5:2] — nHS [3 :0] — номер головки (инверсные биты);

¦ биты [1:0] — nDS [1:0] — выбор устройства (инверсные биты): 10 — выбрано устройство 0, 01 — выбрано устройство 1.

Регистр данных DR (IFOh, 170h) может использоваться как 8-битный или 16-битный в зависимости от типа данных, передаваемых в текущей команде. Обращение к этому регистру происходит в режиме обмена РЮ (когда сигнал DMACK* неактивен), при выполнении передач протокола РО (РЮ Out) хост производит запись в этот регистр, при PI (РЮ In) — чтение.

В режиме DMA обмен данными происходит через порт данных, при этом активны сигналы DMARQ и DMACK*, а сигналы CSO# и CS1# неактивны.

Регистр ошибок ER (IFlh, 171h) хранит состояние выполнения последней операции или диагностический код. После завершения операции на наличие ошибки указывает бит ERR регистра состояния.

Назначение битов регистра ER:

¦ бит 7 — зарезервирован;

¦ бит 6 — UNC (Uncorrectable Data Error) — неисправимая ошибка данных;

¦ бит 5 — МС (Media Changed) — смена носителя (после смены носителя первая команда обращения отвергается и устанавливается данный бит, после сброса бита следующие команды будут выполняться нормальным образом);

¦ бит 4 — IDN F (ID Not Found) — указывает на ненайденный идентификатор сектора;

¦ бит 3 — MCR (Media Change Requested) — индикатор запроса смены носителя (после обнаружения запроса смены носителя команды Door Lock будут возвращать бит ошибки ERR и бит MCR, бит MCR сбрасывается командами Door Unlock, Medi a Ej ect или сигналом аппаратного сброса);

¦ бит 2 — ABRT (Aborted Command) — устанавливается, если команда отвергнута как недействительная или в случае возникновения иной ошибки;

¦ бит 1 —TK0NF (Track ONot Found) —указываетна то, что по команде Recalibrate не удалось найти нулевой трек;

¦ бит 0 — AMNF (Address Mark Not Found) — не найден адресный маркер данных в заголовке сектора.

374________________________________ Глава 9. Интерфейсу устройств хранения

После выполнения любого сброса или команды Execute Device Diagnostic регистр ошибок содержит диагностический код. Трактовка битов, за исключением бита 2 (ABRT), может меняться в зависимости от исполненной команды.

Регистр свойств FR (IFlh, 171h) используется в зависимости от команды. В команде Set Features через него задается код подкоманды. Некоторые старые устройства могут игнорировать запись в этот регистр.

До принятия спецификации АТА-2 в этот регистр помещали значение рекомендуемого номера цилиндра для предкомпен-сации записи.

Регистр счетчика секторов SC (lF2h, 172h) содержит число секторов, участвующих в обмене. Хост инициализирует этот регистр до подачи команды (нулевое значение соответствует 256 секторам). По успешному завершению операции доступа к данным регистр должен обнулиться. Если команда завершилась с ошибкой, в регистре будет число секторов, которые должны быть переданы для успешного завершения предыдущего запроса. Команды Initialize Device Parameters или Write Same могут переопределить значение этого регистра. В некоторых командах регистр используется для передачи иных параметров.

Регистры номера сектора S N (1 F3h, 173h) и номера цилиндра — младшего С L (1 F4h, 174h) и старшего байта СН (lF5h, 175h) — имеют двоякое назначение в зависимости от выбранной системы адресации (CHS или LEA). Они инициализируются хост-адаптером, а в случае возникновения ошибки при выполнении операции устройство поместит в них адрес, по которому встретилась ошибка.

Регистр номера устройства и головки D/H (IFGh, 176h) кроме хранения части адресной информации служит для выбора ведущего или ведомого устройства и метода адресации.

Назначение битов регистра D/H:

¦ биты 7 и 5 вплоть до АТА-3 должны были быть единичными, в AT A/ AT API -4 их объявили устаревшими;

¦ бит 6 — L — единичным значением указывает на применение режима адресации LBA, при нулевом значении бита используется режим CHS;

¦ бит 4 — DEV (Device) — выбор устройства, при DEV=0 выбрано ведущее, при DEV=1 — ведомое;

¦ биты [3:0] имеют двоякое назначение в зависимости от выбранной системы

адресации, в режиме CHS они содержат номер головки, в режиме LBA — старшие биты логического адреса.

Как и предыдущие (5М,СНиС1_), адресный регистр D/H инициализируется хост-адаптером, а в случае возникновения ошибки при операции устройство поместит в них адрес, по которому встретилась ошибка.

До принятия спецификации АТА- 2 считалось, что адресные регистры должны модифицироваться и после успешного выполнения операции, отражая текущее значение адреса в носителе. Регистр состояния S R (l F7h, 177h) отражает текущее состояние устройства в процессе выполнения команд: занятость, готовность, наличие ошибок и др. Чтение регистра состояния разрешает дальнейшее изменение его битов и сбрасывает запрос аппаратного прерывания.

9.2. Интерфейс АТА/ATAPI (IDE) _____________________________________ 375

Назначение битов регистра SR описано ниже.

¦ Бит 7 — BSY (Busy) указывает на занятость устройства, значение этого бита действительно всегда. При BSY=1 устройство игнорирует попытки записи в командный блок регистров, а чтение этих регистров дает неопределенный результат. При BSY=0 регистры командного блока доступны, в это время устройство не может устанавливать бит DRQ, изменять значение битов Е RR и содержимое остальных командных регистров (могут меняться только значения битов IDX, DRDY, DF,

DSC и CORR). Бит может устанавливаться на кратковременный интервал, так что хост может этого не заметить. Бит устанавливается:

• при сбросе устройства;

• по получении команды, если не устанавливается DRQ;

• между передачами блоков данных в режиме РЮ и после них, пока не обнулился DRQ;

• во время передач данных в режиме DMA.

¦ Бит 6 — DRDY (Device Ready) указывает на готовность устройства к восприятию любых кодов команд. Если состояние бита изменилось, оно не может вернуться обратно до чтения регистра состояния. При DRDY=0 устройство воспринимает только команды Execute Device Diagnostic и Initialize Device Parameters, прекращая выполнение текущей команды и сообщая об этом флагом ABRT в регистре ошибок и флагом ERR в регистре состояния. Другие команды приводят к непредсказуемым результатам.

Устройства AT API сбра сывают бит по любому сбросу и команде Execute Device Diagnostic. Бит устанавливается устройством AT A, когда оно готово к выполнению всех команд. Устройство AT API устанавливает бит до завершения выполнения команд, за исключением команд Device Reset и Execute Device Diagnostic.

¦ Бит 5 — DF (Device Fault) — индикатор отказа устройства.

¦ Бит 4 — DSC (Device Seek Complete) — индикатор завершения поиска трека. В командах, допускающих перекрытие, бит называется SERV (Service Required) — устройство требует обслуживания.

¦ Бит 3 — DRQ (Data Request) — индикатор готовности к обмену словом или байтом данных.

¦ Бит 2 — CORR (Corrected Data) — индикатор исправленной ошибки данных.

¦ Бит 1 — I DX (Index) — индекс, трактуется особо каждым производителем.

¦ Бит 0 — ERR (Error) — индикатор ошибки выполнения предыдущей операции.

Дополнительная информация содержится в регистре ошибок. Если установ

лен бит ERR, до приема следующей команды, программного или аппаратного сброса устройство не изменит состояние этого бита, а также регистра ошибок, регистра количества секторов и регистров цилиндра, головки и номера сектора. Для команд PacketnService бит называется СНК и служит признаком исключительной ситуации.

В стандарте ATA/ATAPI-4 для некоторых команд биты 4 и 5 могут иметь иное назначение, а биты 1 и 2 объявлены устаревшими.

376

Глава 9. Интерфейсы устройств хранения

Назначение регистра команд CR (lF7h, 177h) очевидно из названия. Устройство начинает исполнять команду сразу, как только ее код записан в данный регистр. Команда Devi ce Reset выполняется устройством AT API независимо от состояния битов BSY и DRQ, и даже в состоянии Sleep.

Полный список команд АТА приведен в литературе [4,5,9].

Протоколы и режимы передачи данных

Программа общается с устройствами АТА через регистры, используя инструкции ввода-вывода IN и OUT.

Для передачи данных с максимальной скоростью применяют программный доступ РЮ к регистру данных инструкциями INSW/ OUTSW или по каналу DMA. Тип обмена (РЮ или DMA) определяется командой обращения. Программный доступ РЮ обязателен для всех устройств, команды режима DMA устройствами могут не поддерживаться. Параметры различных режимов обмена приведены в табл. 9.7.

Таблица 9.7. Параметры режимов передачи

|

Режим передачи |

Минимальное |

Скорость |

Интерфейс |

|

время цикла, не |

передачи, Мбайт/с |

||

|

РЮ mode 0 |

600 |

3,3 |

АТА |

|

РЮ mode 1 |

383 |

5,2 |

АТА |

|

РЮ mode 2 |

240 |

8,3 |

АТА |

|

РЮ mode 3 |

180 |

11,1 |

E-IDE, АТА-2 |

|

(используется IORDY) |

|||

|

РЮ mode 4 |

120 |

16,6 |

E-IDE, Fast АТА-2 |

|

(используется IORDY) |

|||

|

Singleword DMA Mode 0 |

960 |

2,08 |

АТА |

|

Singleword DMA Mode 1 |

480 |

4,16 |

АТА |

|

Singleword DMA Mode 2 |

240 |

8,33 |

АТА |

|

Multiword DMA Mode 0 |

480 |

4,12 |

АТА |

|

Multiword DMA Mode 1 |

150 |

13,3 |

АТА-2 |

|

Multiword DMA Mode 2 |

120 |

16,6 |

FastАТА-2 |

|

Ultra DMA Mode 0 |

120' |

16,6 |

ATA/ATAPI-4 |

|

Ultra DMA Mode 1 |

80' |

25 |

ATA/ATAPI-4 |

|

Ultra DMA Mode 2 |

601 |

33 |

ATA/ATAPI-4 |

|

Ultra DMA Mode 3 |

451 |

44,4 |

ATA/ATAPI-5 |

|

Ultra DMA Mode 4 |

ЗО1 |

66,6 |

ATA/ATAPI-5 |

|

Ultra DMA Mode 5 |

201 |

100 |

ATA/ATAPI-6 |

Программный доступ РЮ (Programmed Input/Output) выполняется в виде следующих друг за другом операций чтения или записи в пространстве ввода-вывода по адресу регистра данных. Готовность устройства проверяется перед началом

9.2. Интерфейс ATA/ATAPI (IDE)_______________________________________ 377

передачи блока, после чего хост производит серию операций в определенном темпе, который определяется выбранным режимом РЮ Mode 0-4. Для каждого режима определены допустимые параметры временной диаграммы цикла обмена.

Обмен РЮ программно реализуется с помощью процессорных инструкций ввода- вывода строк REP INS или REP OUTS с занесенным в регистр СХ количеством слов (или байтов) в передаваемом блоке. Эти инструкции обеспечивают максимально возможную скорость обмена для данного процессора и системной шины. «Обуздать» процессор в соответствии с выбранным режимом входит в задачу адаптера AT А, который использует для удлинения цикла сигнал готовности шины (для ISA — IOCHRDY). Традиционные режимы 0,1 и 2 имеют временные параметры, фиксируемые только хост-адаптером. Для прогрессивных режимов АТА-2 (РЮ Mode 3 и выше) устройство может затормозить обмен, используя сигнал готовности IORDY. Программный обмен на все время передачи блока занимает и процессор, и системную шину.

Обмен по каналу DMA занимает исключительно шины ввода-вывода и памяти. Процессору требуется выполнить только процедуру инициализации канала, после чего он свободен до прерывания от устройства в конце передачи блока (этим могут воспользоваться многозадачные системы). Стандартные каналы DMA шины ISA для интерфейса АТА не используются из-за низкой пропускной способности. Высокопроизводительные адаптеры АТА имеют собственные более эффективные контроллеры. Режимы обмена по каналу DMA бывают одиночными и множественными. При одиночном режиме — Singleword DMA — устройство для передачи каждого слова вырабатывает сигнал запроса DMARQ и сбрасывает его по сигналу DMACK#, подтверждающему цикл обмена. При множественном режиме — Multiword DMA — на сигнал DMARQ хост отвечает потоком циклов, сопровождаемых сигналами DMACK*. Если устройство не справляется с потоком, оно может приостановить его снятием сигнала DMARQ, а по готовности установить его снова. Множественный режим позволяет развить более высокую скорость передачи.

В спецификации ATA/ATAPI-4 появился новый режим — Ultra DMA, позволяющий перешагнуть барьер в 16,6 Мбайт/с, свойственный традиционным режимам и используемому кабелю. При этом обеспечивается и контроль достоверности передачи данных по шине, чего не делалось ни в РЮ, ни в стандартных режимах DMA (а зря!).

Стандартом АТА-4 было определено 3 режима Ultra DMA (0,1 и 2), впоследствии ввели новые; выбор режима осуществляется командой Set Features. В режимах Ultra DMA сигналы DMARQ и DMACK* сохраняют свое назначение, а вот смысл сигналов DIOR#, DIQW# и IORDY на время передачи пакета (Ultra DMA Burst) существенно меняется. В пакете данные на шине сопровождаются стробом, генерируемым источником данных, причем для синхронизации используются оба перепада сигналов. Это позволяет повысить пропускную способность шины до 33 Мбайт/с, не увеличивая частоту переключения сигналов сверх 8,33 с"1 (этот предел для обычного кабеля достигается в режиме РЮ Mode 4 и Multiword DMA Mode 2). Каждое переданное слово участвует в подсчете CRC-кода, который передается хост-контроллером в конце пакета. Подсчет ведется и источником данных, и приемником.

378________________________________ Глава 9. Интерфейсы устройств хранения

При несовпадении принятого устройством кода с ожидаемым кодом фиксируется ошибка передачи, о которой устройство сообщает в конце исполнения команды. Передача в пакете может приостановиться, если приемник снимет сигнал готовности (DDMARDY* или HDMARDY*). Передача пакета может прекращаться по инициативе устройства (снятием сигнала) или хоста (сигналом STOP). Противоположная сторона должна подтвердить окончание цикла сигналом STOP или DMARQ соответственно.

Способ сообщения об ошибке передачи зависит от типа выполнявшейся команды. Для команд READ DMA,WRITE DMA, READ DMA QUEUED или WRITE DMA QUEUED в регистре ошибок ER устанавливается бит 7 (ICRC) и бит 2 (ABRT). Для пакетной команды REQUEST SENSE (уточнить состояние) в случае ошибки в регистре состояния SR устанавливается бит О (СНК) и сообщается ключ состояния (Sense key) OBh (команда отвергнута). Для всех других пакетных команд в случае ошибки устанавливается бит СНК и сообщается состояние 04h (аппаратная ошибка), а в последующих командах REQUEST SENSE сообщается значениеЛ5С/А5СО 08h/03h (ошибка CRC при связи с логическим устройством).

Получив сообщение об ошибке, хост должен повторить команду. Если ошибки появляются постоянно, хост должен понизить скорость обмена (вплоть до выхода из режима Ultra DMA).

Тип режима обмена определяется возможностями хост-адаптера (и его драйвера), устройств и кабеля, и для каждого устройства он будет ограничен минимумом из максимальных возможностей всех этих компонентов. Как правило, режимы устанавливаются системой автоматически, но пользователю дается возможность при необходимости «подрезать крылья» контроллеру настройками BIOS Setup. Для работы в режимах Ultra DMA Mode 3 и выше требуется 80-проводный кабель, присутствие которого должно быть программно определено до включения этого режима обмена. Правда, в спецификации есть оговорка, что при двухточечном соединении (контроллер—устройство) для режимов 3 и 4 можно использовать 40-проводный кабель (без среднего разъема). Система не должна позволить пользователю применить высокоскоростные режимы на обычном кабеле, при этом желательно, чтобы она сообщала об обнаруженном несоответствии. Для определения типа кабеля есть несколько возможностей [4].

¦ Определение типа кабеля через хост-контроллер, для чего хост-контроллер должен иметь приемник сигнала CBLID*. После включения питания или аппаратного сброса хост ожидает завершения протокола сброса и затем подает команду идентификации Identyf у (Packet) Devi се устройству 1. Устройство 1 стандарта АТА-3 и выше обязано после сброса снять сигнал PDIAG#/CBLID# не позднее, чем по приходу первой команды. Если обнаружено старое устройство, то протокол идентификации кабеля хостом работать не будет (но со старым устройством на шлейфе включать высокоскоростной режим и не стоит). Современное устройство снимет сигнал, и хост-адаптер сможет определить наличие 80-проводного кабеля по низкому уровню CBLID*. Некорректно работающее устройство может удержать низкий уровень сигнала, и в этом случае 40-проводный кабель будет ошибочно трактоваться как 80-проводный.

9-2. Интерфейс АТА/ATAPI (IDE)_______________________________________ 379

¦ Определение типа кабеля через устройство не требует дополнительного при

емника в контроллере — линия PDIAG#/CBLID# в хост-контроллере заземляется через конденсатор емкостью 0,047 мкФ±20 %. Приемник сигнала идентификации кабеля располагается в устройстве. Для определения типа кабеля хост посылает команду Identyf у (Packet) Device устройству 1, чтобы оно освободило линию (сняло сигнал PDIAG*). Затем команда идентификации посылается устройству 0. Примерно через 30 мкс после получения команды устройство кратковременно обнуляет эту линию, затем отпускает и только через 20-30 мкс после этого считывает ее состояние и сообщает его в бите 13 слова 93. Линия подтягивается к +5 В резисторами 10 кОм, установленными в устройствах. Если используется 40-проводный кабель, то конденсатор в хост-адаптере не успеет перезарядиться и устройство сообщит нулевое значение бита. Если кабель 80-проводный, то конденсатор оказывается изолированным от линии PDIAG*/CBLID* в устройстве, и оно сообщит единичное значение бита. Если на хост-контроллере нет конденсатора, то даже 40-проводный кабель будет идентифи

цироваться как 80-проводный, что опасно при передаче данных. Если некор

ректно работающее ведомое устройство своевременно не отпустит линию, то

даже 80-проводный кабель будет казаться 40-проводным.

¦ Комбинированный метод определения типа кабеля предполагает наличие на

хост-контроллере и приемника сигнала CBLID#, и конденсатора (они друг другу не мешают). Решение о наличии 80-проводного кабеля принимается, только если это подтвердят оба метода. Возможная ошибка идентификации будет безопасной — при некорректном устройстве 1 на 80-проводном кабеле не будет включен высокоскоростной режим (наверное, это и к лучшему).

Правильный выбор режима обмена обеспечивает надежность и производительность. Все устройства поддерживают режим РЮ Mode 0, в котором считывается блок параметров идентификации.

В блоке имеются поля, описывающие режим обмена по умолчанию и более эффективные режимы обмена, поддерживаемые устройством. Командой Set Features можно изменить параметры режима. Иногда накопитель не обеспечивает надежной передачи данных в заявленном высокоскоростном режиме. Если данные начинают пропадать, первым делом следует понизить режим обмена.

BIOS определяет режим обмена с каждым устройством с учетом ограничений, заданных в Setup. Старые диски, не сообщающие своих параметров, могут не работать с новыми режимами PIO. На одном ленточном кабеле (канале ATА) могут присутствовать устройства с разным режимом обмена — спецификация это допускает. Однако реально могут возникать аппаратные или программные ограничения. Некоторые чипсеты не позволяют независимо программировать режим обмена для устройств канала. В таком случае при подключении двух разных устройств (например, PIO Mode 1 и 3) обмен с обоими устройствами будет происходить со скоростью меньшего (PIO Mode 1). Поэтому не рекомендуется к одному каналу АТА (порту IDE) подключать быстрый винчестер и медленный CD-ROM. Иногда завязка режимов обмена двух устройств обусловлена ограниченным набором параметров конфигурации в BIOS. Быстрые режимы множественного обмена по

380________________________________ Глава 9. Интерфейсы устройств хранения

DMA реализуются только драйверами ОС. «Глупый» драйвер может попытаться навязать медленный режим обоим устройствам канала, так что смешивать разные устройства не стоит и по этой причине.

Протокол обмена PIO хорош только для однозадачных ОС. Для многозадачных ОС больший интерес представляет обмен по протоколу DMA, если, конечно, поддерживаемый режим обеспечивает приемлемую скорость обмена. С точки зрения драйвера есть различия лишь между типами режимов (РЮ, DMA и UltraDMA); аппаратные нюансы режимов внутри типа влияют только на скорость передачи. Режим UltraDMA значительно отличается от обычного DMA необходимостью обработки возможных ошибок передачи по шине; в случае постоянных ошибок драйвер должен понизить режим UltraDMA (вплоть до перехода на традиционные режимы).

Протокол взаимодействия хоста с устройством выглядит следующим образом.

1. Хост читает регистр состояния устройства, дожидаясь нулевого значения бита В S Y.Если присутствуют два устройства, хост обращается к ним «наугад» — состояние будет сообщаться последним выбранным устройством.

2. Дождавшись освобождения устройства, хост записывает в регистр D/H байт,у которого бит DEV указывает на адресуемое устройство. Здесь кроется причина невозможности параллельной работы двух устройств на одной шине AT А:обратиться к устройству можно только после освобождения обоих устройств.

3. Хост читает основной или альтернативный регистр состояния адресованного

устройства, дожидаясь признака готовности (DRDY=1).

4. Хост заносит требуемые параметры в блок командных регистров.

5. Хост записывает код команды в регистр команд.

6. Устройство устанавливает бит BSY и переходит к исполнению команды.

Дальнейшие действия зависят от протокола передачи данных, заданного командой.

Для команд, не требующих передачи данных, следующий шаг (шаг 7) — последний. Завершив исполнение команды, устройство сбрасывает бит BSY и устанавливает запрос прерывания (если он не запрещен). К этому моменту в регистрах состояния и ошибок уже имеется информация о результате исполнения. Единичное значение бита BSY может «промелькнуть» между шагами 6 и 7 так быстро, что хост его не зафиксирует, но для фиксации факта выполнения команды или ее части предназначен запрос прерывания.

Для команд, требующих чтения данных в режиме РЮ, процедура продолжается следующим образом.

7. Подготовившись к передаче первого блока данных по шине АТА, устройство

устанавливает бит DRQ. Если была ошибка, она фиксируется в регистрах состояния и ошибок. Далее устройство сбрасывает бит BSY и устанавливает запрос прерывания (если он не запрещен).

8. Зафиксировав обнуление бита BSY (или по прерыванию), хост считывает регистр состояния, что приводит к сбросу прерывания от устройства.

9.2. Интерфейс АТА/ATAPI (IDE)_______________________________________ 381

9. Если хост обнаружил единичное значение бита DRQ, он производит чтение первого блока данных в режиме PIO (адресуясь к регистру данных). Если обнаружена ошибка, считанные данные могут быть недостоверными. После передачи блока данных возможно одно из следующих действий:

• если на шаге 8 ошибка не обнаружена и требуется передача следующего

блока, устройство устанавливает бит BSY и данная последовательность повторяется с шага 7;

• если есть ошибка или передан последний блок данных, устройство сбрасы

вает бит DRQ и выполнение команды завершается.

Для операций записи данных после шага б для устройства начинается активная фаза записи на носитель, что отмечается установкой бита BSY.

Для команд, требующих записи данных в режиме PIO, процедура после шага 6 продолжается следующим образом.

7. Подготовившись к приему первого блока данных по шине ATА, устройство устанавливает бит DRQ (если нет ошибок) и сбрасывает бит B5Y. Если была ошибка, она фиксируется.

8. Зафиксировав обнуление бита BSY, хост считывает регистр состояния.

9. Если хост обнаружил единичное значение бита DRQ, он производит запись первого блока данных в режиме PIO по адресу в регистре данных.

10. После передачи блока данных возможно одно из следующих действий:

• если обнаружена ошибка, устройство сбрасывает бит DRQ, устанавливает запрос прерывания и выполнение команды завершается, а переданные по шине данные остаются устройством необработанными (не записываются на носитель);

• если ошибка не обнаружена, устройство устанавливает бит BSY и переходит к следующему шагу.

11. Устройство обрабатывает принятый блок данных, затем:

• если нет ошибок и обработанный блок — последний, устройство сбрасывает бит B5Y и устанавливает запрос прерывания, на чем выполнение команды успешно завершается;

• если обнаружена ошибка, выполнение команды завершается таким же об

разом, но с установкой битов ошибок;

• если нет ошибок и требуется передача следующего блока, процедура про

должается.

12. По готовности приема следующего блока устройство устанавливает бит DRQ, сбрасывает бит BSY и устанавливает запрос прерывания.

13. По обнулении бита BSY (или по прерыванию) хост считывает регистр состояния.

14. Обнаружив бит DRQ, хост выполняет запись очередного блока в регистр данных, и последовательность повторяется с шага 11.

382________________________________ Глава 9. Интерфейсы устройств хранения

Команды с передачей данных в режиме DMA выполняются похожим образом, но с некоторыми исключениями.

¦ Вместо PIO используется прямой доступ к памяти. Хост должен инициализи

ровать канал DMA до записи кода в регистр команд, чтобы при появлении сигнала DMARQ начался обмен.

¦ Запрос прерывания даже в многосекторных передачах производится один

раз — по выполнении команды.

Адаптеры и контроллеры шины АТА

Простейший адаптер АТА содержит только буферы сигналов шины и дешифратор зоны адресов. Все регистры контроллера и схемы кодирования размещены в самом устройстве IDE. Шина АТА требует выделения системных ресурсов — двух областей портов ввода-вывода и линии прерывания; дополнительно может потребоваться канал DMA. Интерфейсу АТА первого канала выделили ресурсы, ранее использовавшиеся контроллером жестких дисков. Второму каналу назначили ресурсы альтернативного контроллера жестких дисков. Позже определили ресурсы еще для двух каналов (табл. 9.8). Традиционному контроллеру жестких дисков выделялся канал DMA3, но он является 8-битным, в то время как шина АТА требует 16-битного канала DMA. Производительности стандартных каналов DMA для шины АТА явно недостаточно.

Таблица 9.8. Системные ресурсы каналов АТА

Канал CSO CS1 IRQ

|

1 |

1FOh-1F7h |

3F6h-3F7h |

14 |

|

2 |

170h-177h |

376h-377h |

15или 10 |

|

3 |

1E8h-1Efh |

3Eeh-3Efh |

12 или 11 |

|

4 |

168h-16Fh |

36Eh-36Fh |

10 или 9 |

¦ В каждом канале должны быть собственные формирователи управляющих сигналов DIOR#, DIOW# и приемник IORDY (рекомендуемый вариант); либо должны быть раздельные формирователи CSO# и CS1# (второй вариант логичнее, но хуже в плане помех). Такая конфигурация позволяет использовать все режимы обмена, кроме Ultra DMA.

9.2. Интерфейс АТА/ATAPI (IDE)

383

¦ Для поддержки Ultra DMA 0,1 и 2 (до 33 Мбайт/с) к этим требованиям добав

ляется наличие раздельных формирователей сигнала DMACK#.

¦ Для поддержки Ultra DMA 3 и выше (44-100 Мбайт/с) все линии должны

иметь раздельные приемопередатчики. Общими могут быть только сигналы

RESET*, INTRQ, DA(2:0), CSO#, CS1# и DASP#, но стандарт этого не рекомендует.

Поскольку скорость программного обмена задается хост-адаптером, интересно индивидуальное программирование режимов РЮ Mode для каждого канала/устройства.

Ряд чипсетов этого не допускает и при инициализации назначает общий минимальный режим. В результате подключение «тихоходного» устройства замедляет обмен быстрого соседнего устройства.

Современные системные платы оснащаются высокопроизводительными контроллерами шины AT А, обеспечивающими прямое управление шиной PCI (bus mastering) при обмене с устройствами в режимах DMA и Ultra DMA. Прямое управление шиной повышает суммарную производительность компьютера в многозадачных и многопоточных операционных системах. Сами по себе режимы DMA не дают выигрыша в скорости обмена по шине АТА — только режимы UltraDM A Mode 1 и выше превосходят по скорости режим РЮ Mode 4 (см. табл. 9.7). Однако обмен в режиме DMA значительно меньше загружает центральный процессор компьютера, и параллельно с дисковым обменом процессор может заниматься обработкой других потоков (задач). В однозадачных (и однопоточных) системах во время дискового обмена процессор все равно ничем другим не занимается, поэтому для них хорош и режим РЮ Mode. Для реального использования режима прямого управления в операционной системе должен быть установлен специальный драйвер Bus-Master, соответствующий используемому контроллеру АТА (как правило, чипсету системной платы). Стандартный контроллер PCI IDE описан ниже. Операционная система MS-DOS режимы DMA (и прямое управление) не использует. Для многозадачных ОС (Windows 9x/NT/2000, OS/2, Unix, Linux, NetWare...) драйверы могут входить в комплект поставки ОС или поставляться производителями системных плат (контроллеров АТА). И наконец, режим DMA должны поддерживать подключаемые устройства. Практически все современные устройства поддерживают Ultra DMA (или Multiword DMA), но если в паре с таким устройством к одному контроллеру подключено старое устройство, не поддерживающее этот режим, то прогрессивные режимы могут оказаться недоступными (по вине чипсета или драйвера) и для нового устройства.

ВНИМАНИЕ---------------------------------------------------------------------------------

Режим UltraDMA привлекателен не только скоростью и разгрузкой процессора, но и контролем достоверности передач по шине АТА (правда, этот контроль корректно работает не со всеми драйверами).

384_____________________________ Глава 9. Интерфейсы устройств хранения

Более сложные контроллеры (отдельные карты расширения) могут иметь собственную кэш-память и управляющий процессор. Они могут аппаратно поддерживать «зеркальные» диски и организовывать RAID-массивы АТА-дисков. Некоторые адаптеры позволяют соединять несколько физических дисков в один логический на уровне вызовов BIOS.

Адаптеры АТА одно время часто размещали на звуковых картах (для подключения CD-ROM). По умолчанию им назначают ресурсы канала 3 или 4. К этим каналам можно подключать винчестеры, но будет ли их там искать BIOS во время теста POST — вопрос. Современные версии BIOS позволяют хранить конфигурационные параметры четырех жестких дисков, более старые версии — двух. Четыре канала АТА физически позволяют подключить до восьми накопителей, но работа с ними лимитирована программными ограничениями.

Существуют гибридные адаптеры для подключения АТА HDD к шинам XT и МСА или, например, к LPT-порту. В последнее время получили распространение переходные адаптеры, позволяющие подключать устройства AT A/ AT API к шине USB. При использовании USB 2.0 простота подключения внешнего устройства будет сочетаться и с высокой скоростью передачи данных.

Контроллер PCI IDE

Для шины PCI существует стандартный вариант интерфейса контроллера IDE (название «АТА» здесь не очень уместно, поскольку оно ориентировано на ISA-подобную шину).

Спецификация « PCI IDE Controller Specification» появилась еще в 1994 году, она описывала реализацию контроллера, совместимого с интерфейсом АТА. По сравнению с обычным контроллером, у данного контроллера в блоке управляющих регистров имеется лишь один адрес (устаревший регистр адреса недоступен). Чуть позже была опубликована спецификация «Programming Interface for Bus Master IDE Controller», описывающая работу с устройствами в режиме DMA с прямым управлением шиной. Двухканальный контроллер является одной функцией PCI; четырехканальный контроллер будет уже многофункциональным устройством PCI. Для контроллера определены два режима распределения ресурсов:

¦ режим совместимости (compatibility), в котором каналам выделяются тради

ционные области адресов ввода-вывода и линии прерываний;

¦ естественный режим PCI (native-PCI), в котором базовые адреса блоков регистров и линии прерывания задаются в регистрах конфигурационного пространства и могут быть произвольно перемещаемы в любую область.

Распределение ресурсов для контроллера приведено в табл. 9.9. В режиме совместимости контроллер может работать только на первичной шине PCI, поскольку мост PCI-PCI не будет транслировать обращения по стандартным адресам на другую шину. В режиме PCI с перемещаемыми ресурсами контроллер может находиться на любой шине. Конкретный контроллер может поддерживать изменение режима или один из режимов. Если контроллер по умолчанию (или всегда) работает в режиме совместимости, то для ПО он «прозрачен» — работа с ним не отличается от традиционного контроллера АТА. Текущий режим и возможность

9.2. Интерфейс ДТА/ATAPI (IDE)_______________________________________ 385

его смены отражается в байте программного интерфейса, являющегося последним элементом идентификатора класса устройства. Байт интерфейса имеет следующее назначение битов:

¦ бит 7 (bus mastering) — возможность работы в режиме прямого управления;

¦ биты 6:4 — 000 ( признак стандартного интерфейса, соответствующего PCI IDE Controller Specification);

¦ бит 3 — индикатор программируемое™ режима для второго канала (возможности изменения бита 2);

¦ бит 2 — режим второго канала: 0 — совместим со стандартным контроллером ATA IDE, 1 - PCI IDE;

¦ бит 1 — индикатор программируемости режима для первого канала (возможности изменения бита 0);

¦ бит 0 — режим первого канала: 0 — совместим с ATA IDE, I — PCI IDE.

Таблица 9.9. Ресурсы контроллера PCI IDE

ресурсы для каналов базовый адрес (смещение

в конфигурационном пространстве) для канала

12 12

|

Блок командных регистров |

1FOh-1F7h |

170h-177h |

10h |

14h |

|

Блок управляющих регистров |

3F6h |

376h |

18h |

1Ch |

|

Прерывание |

14 |

15 |

В итоге после конфигурирования во время POST при обращении программ к устройствам остается выбор лишь между РЮ и DMA (если устройство поддерживает DMA). Для обмена в режиме РЮ никаких специальных действий не требуется, программа просто выполняет чтение или запись в регистр данных командами REP IN5/OUTS. Для обмена в режиме DMA требуется «зарядить» и запустить контроллер прямого управления, о чем и пойдет речь ниже.

386________________________________ Глава 9. Интерфейсы устройств хранения

Двухканальный контроллер имеет 16-байтный блок регистров, расположенный в пространстве портов ввода-вывода. Базовый адрес блока хранится в конфигурационном пространстве устройства по смещению 20h (берутся младшие 16 бит двойного слова). Расположение регистров в блоке показано в табл. 9.10, имена регистров имеют префикс BMI (Bus Master IDE) и окончание Р (Primary) для первого канала, S (Secondary) — для второго; в описании будем использовать окончание х (любой канал).

Таблица 9.10. Блок регистров контроллера PCI IDE

J________ 2________________________________________________________________________

0 8 1 BMICP/BMICS (RW) — регистр команд: бит 0:

1 — запуск, 0 — останов; бит 3 — направление: 0 — чтение памяти, 1 — запись в память; биты 1 -2, 3-7 — резерв (0)

1 9 1 Резерв (0)

2 OAh 1 BMISP/BMISS— регистр состояния: бит 0 (R/O) —

активность канала; бит 1 (RWC) — ошибка обмена по PCI; бит 2 (RWC) — запрос прерывания от устройства; биты 3-4 — резерв (0); бит 5 (RW) — устройство 0 поддерживает DMA; бит 6 (RW) — устройство 1 поддерживает DMA; бит 7 — признак симплексного режима (1, если каналы не могут работать одновременно)

3 OBh 1 Резерв (0)

4 ОСИ 4 BMIDPTP/BMIDPTS(RW)— адрес таблицы

дескрипторов

В регистре состояния BMISx биты 1 и 2 устанавливаются аппаратно, а сбрасываются при записи байта с единичным значением в соответствующем бите. После сброса бита запроса прерывания он снова установится только по следующему фронту сигнала прерывания от устройства. Биты 5 и 6 устанавливаются программно, обычно когда POST определяет возможности подключенных устройств и программирует режимы контроллера. Регистр состояния должен быть прочитан после завершения выполнения команды для определения успешности операций на шине PCI. В регистр ВМI DPTx заносят адрес таблицы дескрипторов областей памяти, с которыми производится обмен данными. Контроллер способен при чтении памяти собрать поток данных из произвольного числа областей (gathered read), а при записи «разбросать» поток по этим областям (scatter write). Такая возможность ветре-

9.2. Интерфейс ДТА/ATAPI (IDE)_______________________________________ 387

чалась еще в EISA-системах, она позволяет преодолевать барьеры на границах страниц, свойственные стандартным контроллерам DMA и страничной переадресации процессоров х86.

Каждый дескриптор занимает 8 байтов:

¦ байты 0-3 (двойное слово) — физический адрес начала области (четный);

¦ байты 4-5 (слово) — счетчик байтов (четный, 0000 соответствует 65 536);

¦ байты 6-7 (слово) — признак конца таблицы (бит 15), биты 0-14 не используются (0).

Каждая область может быть расположена в произвольном месте памяти (кроме отображаемой на шину ISA) и иметь произвольный размер, но не должна пересекать границы страниц размером 64 Кбайт. Таблица дескрипторов должна быть выровнена по границе двойного слова и не должна пересекать границы страниц, имеющих размер 64 Кбайт. Число дескрипторов в таблице произвольно, последний должен содержать признак конца таблицы. Обмен начинается с области, описанной первым дескриптором; за ней идет область следующего дескриптора и так далее до последнего. Контроллер остановится по исчерпании счетчика в последнем дескрипторе или по инициативе устройства, если в обмене должно участвовать меньшее число данных. Если устройству данных не хватит, оно укажет на ошибку при завершении команды.

После запуска контроллера второй и нулевой биты регистра состояния отражают следующие ситуации:

¦ 0,1 — происходит обмен с памятью, прерывания по концу операции еще нет;

¦ 1,0 — обмен завершен, переданный объем соответствует объему описанных буферов (нормальное завершение);

¦ 1,1 — устройство завершило обмен, но по команде АТА передано меньше данных, чем описано в таблицах (допустимое завершение);

¦ 0,0 — ошибка на шине (бит 1), или в таблицах описано меньше данных, чем в команде АТА.

Конфигурирование устройств

Устройства АТА перед подключением к шине должны быть корректно сконфигурированы. Конфигурирование подразумевает выбор типа интерфейса и определение адреса устройства. Тип интерфейса — XT или AT — определяется моделью накопителя.

В изделиях фирмы Seagate, например, тип обозначается последней буквой в шифре модели: А — АТА (16 бит,) X — для XT (8 бит), а сочетание АХ означает возможность выбора AT/XT с помощью джампера.

Существует два способа задания адреса устройства — кабельной выборкой или явным заданием адреса на каждом из устройств. Режим кабельной выборки включается перемычкой CS (Cable Select — кабельная выборка). В этом случае оба устройства на шине конфигурируются одинаково — в режим CS, а адрес устройства определяется его положением на специальном ленточном кабеле (см. рис. 9.3). Кабельная выборка будет работать, если она поддерживается и задана на всех

388________________________________ Глава 9. Интерфейсы устройств хранения

устройствах канала, включая хост-адаптер, который обеспечивает заземление контакта 28. При этом способе задания адресов синхронизация шпинделей накопителей через тот же провод контакта 28 исключается (актуально в RAID-массивах). Кабельная выборка применяется редко. Ее условное преимущество — унификация конфигурирования устройств, а недостатком является привязка физического положения устройств к кабелю — ведущее устройство должно быть ближе к адаптеру, чем ведомое. Возможно подключение адаптера к среднему разъему, а устройств — к крайним, но это не всегда удобно.

Более распространен режим явной адресации, при котором используется обычный «прямой» кабель (см. рис. 9.2). В этом случае перемычка CS не устанавливается, а адрес устройства задается перемычками, состав которых варьируется. В принципе, достаточно лишь указать устройству его номер (0/1), но в устройствах, разработанных до стандарта AT А, ведущему устройству «подсказывали» о наличии ведомого (по интерфейсу АТА оно могло бы определить это само по сигналу DASP#). Ниже перечислены комбинации джамперов, которые можно увидеть на устройствах IDE.

¦ M/S (Master/Slave — ведущее/ведомое) — переключатель адреса. Если на шине присутствует одно устройство, оно должно быть сконфигурировано как ведущее.

Если на шине два устройства — одно должно быть ведущим, другое ведомым. Иногда джампер обозначается как C/D (диск С:/диск D:), но для второго канала IDE такое название некорректно. Когда появились первые IDE-диски емкостью 1 Гбайт, для преодоления барьера в 504 Мбайт некоторые модели допускали конфигурирование в виде двух устройств (0 и 1) половинной емкости. В таком режиме на их ленточный кабель IDE второе физическое*устройство подключать нельзя.

¦ SP (Slave Present), DSP (Drive Slave Present), Master but Slave is not ATA-compatible или Master but Slave uses only PDIAG-signal — устанавливается на ведущем устройстве для указания на присутствие ведомого. Если переключатель установлен, а ведомое устройство не подключено, POST даст сообщение об ошибке. Джампер применяется для дисков, не использующих сигнал DASP*.

¦ Single Drive — джампер, устанавливаемый на устройстве, если оно единственное на шине (встречается на дисках Western Digital). Устройство будет ведущим.

¦ ACT (Drive Active) — джампер, соединяющий линию DASP* с формирователем сигнала активности устройства. Устанавливается на устройстве 0, встречается редко.

¦ HSP — джампер, заземляющий линию DASP* (положение, взаимоисключающее ACT). Устанавливается на устройстве 1 для сигнализации о его присутствии (встречается редко).

Для полностью ATА-совместимых дисков правильно сконфигурированные устройства определяются автоматически. Современные контроллеры АТА позволяют подключать даже единственное устройство как ведомое —интерфейсные функции ведущего берет на себя контроллер.

9.2. Интерфейс АТА/ATAPI (IDE)_______________________________________ 389

Разобраться с джамперами старых устройств трудно, если нет документации, однако обширная база данных по разным моделям встроена в справочный файл утилиты Disk Manager. У современных устройств лишние джамперы упразднили, а существующие комментируются на наклейке (шильдике).Если джамперы устанавливаются рядом с интерфейсным разъемом, вероятно, они расположены в соответствии со стандартом АТА (см. рис. 9.5).

ВНИМАНИЕ---------------------------------------------------------------------------------

Следует учитывать, что перестановка джамперов часто воспринимается устройством только по включении питания. Кроме того, установка на один ленточный кабель двух разнотипных устройств, если они не являются АТА-устройствами, часто невозможна.