EEPROM и флэш-память

Электрически стираемая (и перезаписываемая) память EEPROM, или E2PROM (Elecrical Erasable PROM), отличается простотой выполнения записи. В простейшем (для пользователя) случае программирование сводится к записи байта по требуемому адресу, после чего некоторое время микросхема не способна выполнять операции чтения/записи и по другим адресам, вплоть до окончания выполнения внутренней операции программирования (со встроенным стиранием). Микросхемы могут поддерживать и режим страничной записи (Page Write), в котором они принимают поток байт записи смежных ячеек в страничный буфер на нормальной скорости интерфейса, после чего вся страница записывается в энергонезависимую память. Страничная запись экономит время (запись страницы выполняется за то же время, что и одной ячейки), но размер страничного буфера, как правило, небольшой (4-32 байт для микросхем небольшого объема и до 128-256 байт — большого). Более сложный интерфейс записи использует систему команд, в которую могут входить команды разрешения/запрета стирания и записи, стирание (отдельной ячейки или всей памяти), запись. Микросхема может иметь и специальные внутренние регистры, например регистр состояния, определяющий готовность микросхемы к обмену данными и возможные режимы защиты от модификации ячеек. Некоторые старые микросхемы для стирания требуют подачи сравнительно высокого (12 В) напряжения на определенные выводы. По процедуре программирования некоторые микросхемы EEPROM схожи с флэш-памятью. В настоящее время EEPROM применяются наряду с флэш-памятью, причем они могут соседствовать даже в одной микросхеме (например, микроконтроллере). Это объясняется очень большим гарантированным числом циклов перезаписи (106 и более) EEPROM, но меньшим достижимым объемом. Также EEPROM обычно имеет и большее гарантированное время сохранности информации (до 100 лет). Флэш-память при большем объеме и более производительных способах записи и стирания допускает меньшее число циклов перезаписи, и время сохранения информации у нее меньше (может быть и всего 10 лет).

Микросхемы EEPROM выпускаются с различными интерфейсами, последовательными (Serial EEPROM) с интерфейсами PC, SPI и иными и параллельными (Parallel EEPROM) с интерфейсами статической памяти (и EPROM).

Флэш-память по определению относится к классу EEPROM (электрическое стирание), но использует особую технологию построения запоминающих ячеек. Стирание во флэш-памяти производится сразу для целой области ячеек (блоками или полностью всей микросхемы). Это позволило существенно повысить производительность в режиме записи (программирования). Флэш-память обладает сочетанием высокой плотности упаковки (ее ячейки на 30 % меньше ячеек DRAM), энергонезависимого хранения, электрического стирания и записи, низкого потребле-

7.3. Энергонезависимая память________________________________________ 283

ния, высокой надежности и невысокой стоимости. Первые микросхемы флэш-памяти были предложены фирмой Intel в 1988 году и с тех пор претерпели существенные изменения по архитектуре, интерфейсу и напряжению питания. Каждая ячейка флэш-памяти состоит всего из одного униполярного (полевого) транзистора. Ячейки организованы в матрицу; разрядность данных внешнего интерфейса — 8 или 16 бит (ряд микросхем имеет переключаемую разрядность). Чистые (стертые) ячейки содержат единицу во всех битах; при записи (программировании) нужные биты обнуляются. Возможно последующее программирование и уже записанных ячеек, но при этом можно только обнулять единичные биты, но не наоборот. В единичное состояние ячейки переводятся только при стирании. Стирание выполняется для всей матрицы ячеек; стирание одиночной ячейки невозможно. Чтение флэш-памяти ничем не отличается от чтения любой другой памяти — подается адрес ячейки, и через некоторое время доступа (десятки-сотни не) на выходе появляются данные. Запись выглядит несколько сложнее — для программирования каждого байта (слова) приходится выполнять процедуру, состоящую из операций записи и считывания, адресованных к микросхеме флэш-памяти.

Одна ко при этом шинные циклы обращения к микросхеме являются нормальными для процессора, а не растянутыми, как для EPROM и EEPROM. Таким образом, в устройстве с флэш-памятью легко реализуется возможность перепрограммирования без извлечения микросхем из устройства. Большинство микросхем флэш-памяти имеют интерфейс, аналогичный асинхронной статической памяти (SRAM), а при чтении он упрощается до интерфейса ROM/PROM/EPROM. Существуют версии с интерфейсом динамической памяти, асинхронным и синхронным, а также и со специальными интерфейсами, в том числе и 12С. Первые микросхемы работали только при напряжении питания 5 В, а для программирования и стирания требовали дополнительное питание VPP = +12 В. Затем появились микросхемы всего с одним напряжением питания +5 В. Дальнейшее развитие технологии позволило снизить напряжение питания до 2,7-3,3 В и 1,65-2,2 В, a VPP — до 5, 3,3, 2,7 и даже 1,65 В. В производстве микросхем используется технологические процессы с разрешением 0,3, 0,22, 0,18 мкм (чем мельче ячейки, тем они экономичнее). Микросхемы первых выпусков (1990 г.) имели гарантированное число циклов стирания-программирования 10 000, современные — 100 000.

Флэш-память имеет время доступа при чтении 35-200 не. Стирание информации (поблочное или во всей микросхеме) у микросхем середины 90-х годов занимает 1-2 секунды, программирование (запись) байта — порядка 10 мкс. У современных микросхем время стирания и записи заметно сократилось. Процедура записи от поколения к поколению упрощается (см. ниже). От ошибочного стирания (записи) применяются различные методы программной и аппаратной защиты. Программной защитой является ключевая последовательность команд, нарушение которой не позволяет начать операции стирания и записи. Аппаратная защита не позволяет выполнять стирание и запись, если на определенные входы не поданы требуемые уровни напряжения. Аппаратная защита может защищать как весь массив целиком, так и отдельные блоки.

По организации массива в плане стирания групп ячеек различают следующие архитектуры:

¦ Bulk Erase (BE) — все ячейки памяти образуют единый массив; запись воз

можна в произвольную ячейку; стирание возможно только для всего объема

сразу;

¦ Boot Block (BB) — массив разделен на несколько блоков разного размера, стираемых независимо, причем один из блоков имеет дополнительные средства защиты от стирания и записи;

¦ Flash File — массив разделен на несколько равноправных независимо стираемых блоков обычно одинакового размера, что позволяет их называть микросхемами с симметричной архитектурой (Symmetrical Architecture, SA).

Организация BE применялась только в микросхемах первого поколения, ее недостатки вполне очевидны (получается просто аналог EEPROM с более удобным способом стирания и интерфейсом программирования). Все современные микросхемы секторированы (разбиты на отдельно стираемые блоки), так что остается лишь деление на симметричную и несимметричную архитектуру.

В симметричной архитектуре (SA), как правило, используется разбиение на блоки по 64 Кбайт; один из крайних блоков (с самым большим или самым маленьким адресом) может иметь дополнительные средства защиты.

В асимметричной архитектуре один из 64-килобайтных блоков разбивается на 8 блоков по 8 Кбайт. Один из блоков имеет дополнительные аппаратные средства защиты от модификации и предназначается для хранения жизненно важных данных, не изменяемых при запланированных модификациях остальных областей. Эти микросхемы специально предназначены для хранения системного программного обеспечения (BIOS), а привилегированный блок (Boot Block) хранит минимальный загрузчик, позволяющий загрузить (например, с дискеты) и выполнить утилиту программирования основного блока флэш-памяти. В обозначении этих микросхем присутствует суффикс Г (Тор) или В (Bottom), определяющий положение Boot-блока либо в старших, либо в младших адресах соответственно.

Первые предназначены для процессоров, стартующих со старших адресов (в том числе, х86, Pentium), вторые — для стартующих с нулевого адреса, хотя возможны и противоположные варианты, когда некоторые биты шины адреса перед подачей на микросхему памяти инвертируются. Старые микросхемы В В малого объема имели немного другое распределение, например микросхема 28F001ВХ- Т (28F001BN- Т), часто применяемая для флэш-BIOS в PC, содержит:

¦ основной блок (Main Block) объемом 112 Кбайт (OOOOOh-lBFFFh);

¦ два блока параметров (Parameter Block) объемом по 4 Кбайт (1 COOOh-1 CFFFh и IDOOOh-lDFFFh);

¦ загрузочный блок (Boot Block) объемом 8 Кбайт (lEOOOh-lFFFFh), стирание и программирование которого возможны лишь при особых условиях.

7.3. Энергонезависимая память __________________________ 285

Основной блок и блоки параметров по защите равноправны; выделение небольших блоков параметров позволяет в них хранить часто сменяемую информацию, например ESCD технологии PnP.

Выпускают и комбинированные микросхемы, например MT28C3214P2FL представляет собой комбинацию флэш-памяти 2 М х 16 и SRAM 256 К х 16. По организации матрицы ячеек различают архитектуры NOR и NAND. В традиционной организации NOR транзисторы на одном проводе объединяются своими стоками параллельно, как бы образуя логический элемент ИЛИ-НЕ (NOR — Not OR). Эта организация обеспечивает высокое быстродействие произвольного считывания, что позволяет исполнять программы прямо из флэш-памяти (не копируя в ОЗУ) без потери производительности. В организации NAND несколько транзисторов разных ячеек соединяются последовательно, образуя логический элемент И-НЕ (NAND — Not AND), что дает высокую скорость последовательных обращений.

В первых микросхемах флэш-памяти каждая ячейка (всего один транзистор) предназначалась для хранения одного бита информации (1 — стерта, 0 — «прошита»). Позже появилась технология хранения двух битов в одной ячейке — благодаря совершенствованию технологии удалось надежно различать 4 состояния ячейки, что и требуется для хранения двух битов.

Два бита в ячейке хранит память Intel StrataFlash, емкость одной такой микросхемы уже достигла 128 Мбит (16 Мбайт).

Флэш-память постоянно развивается как в плане повышения емкости и снижения потребления, так и в плане расширения возможностей и повышения производительности. Так, например, в ряде микросхем AMD имеется возможность чтения одновременно с записью других блоков (чтение во время стирания стало возможным еще со второго поколения флэш-памяти).

Некоторые микросхемы обеспечивают быстрый обмен в страничном режиме (Page Mode). Страницей являются 4 или 8 смежных ячеек; первое чтение в странице выполняется со временем доступа 70 не. Если микросхема остается выбранной, то другие ячейки этой страницы (отличающиеся значением младших битов адреса) можно считывать циклами длительностью по 20 не. Доступ к одиночным ячейкам не отличается от обычного. Микросхемы с пакетным режимом (Burst Mode) вдобавок к одиночному и страничному режимам (асинхронным) могут работать и в синхронном режиме. Для этого они имеют вход синхронизации CLK. Адрес начала пакета передается вместе с сигналом ADV# (фиксируются по положительному перепаду CLK). Первые данные на выходе появятся через 3 такта, после чего в каждом следующем такте будут выдаваться очередные данные.

Синхронная флэш-память имеет интерфейс (и даже упаковку в корпуса), совпадающий с SDRAM. В настоящее время выпускаются микросхемы с частотой 66 МГц (например, MT28S4M16LC — 1 М х 16 х 4 банка), ожидаются микросхемы и на 133 МГц. Такая память удобна для встраиваемых компьютеров для хранения ПО, исполняемого прямо на месте (без копирования в ОЗУ).

286________________________________ Глава 7. Интерфейсы электронной памяти

Микросхемы флэш-памяти с симметричной архитектурой выпускаются и с интерфейсом DRAM (динамической памяти) — с мультиплексированной шиной памяти, стробируемой сигналами RAS# и CAS#. Они предназначены для применения в модулях SIMM или DIMM, устанавливаемых в гнезда для обычной динамической памяти.

Таким образом реализуются, например, модули PostScript для лазерных принтеров и любые резидентные программные модули. Эти модули, естественно, не будут определяться системой как основная память — на попытку обычной записи и считывания, предпринимаемую в тесте POST при определении установленной памяти, они ответят весьма своеобразно. Также они не будут восприниматься и как модули дополнительной системы BIOS, поскольку займут неподходящие для этого физические адреса. Использоваться эти модули смогут только с помощью специального драйвера, который «объяснит» чипсету, какому диапазону адресов пространства памяти соответствуют сигналы выборки банков флэш-памяти. Поскольку интерфейс модулей SIMM и DIMM не предполагает сигналов защиты записи, системного сброса и дополнительного питания +12 В, все вопросы, связанные с программированием и защитой, решаются дополнительными элементами, устанавливаемыми на модулях. При использовании 16-битных микросхем такие модули непосредственно не обеспечивают независимую побайтную запись, но она может обеспечиваться программно, маскированием (записью OFFh) немодифицируемых байт.

Для хранения BIOS появились микросхемы флэш-памяти с интерфейсом LPC, называемые хабами (firmware hub).

Для некоторых сфер применения требуются специальные меры по блокированию изменения информации пользователем. Так, Intel в некоторые микросхемы вводит однократно записываемые регистры ОТР (One-Time-Programmable). Один 64-битный регистр содержит уникальный заводской номер, другой может программироваться пользователем (изготовителем устройства) только однажды.

Фирма Intel выпускает микросхемы «Wireless Flash Memory» — за интригующим названием скрывается, конечно же, «нормальный» электрический интерфейс с проводами (wireless — без проводов). Однако они ориентированы на применение в средствах беспроводной связи (сотовые телефоны с доступом к Интернету): питание 1,85 В, наличие регистров ОТР для защиты от мошенничества и т.

п.

Корпуса, интерфейс и обозначение микросхем флэш-памяти

Микросхемы флэш-памяти упаковывают в корпуса со стандартизованным назна чением выводов. Первые микросхемы выпускались в корпусах DIP, что обеспечивало легкость замены микросхем (E)EPROM на флэш-память. Далее в целях миниатюризации перешли к корпусам PLCC, TSOP и TSOP-II. Применение корпусов FBGA (Fine Pitch Ball Grid Array) — матрицы 6x8 шариковых выводов с шагом 0,8 мм — позволяет уменьшить размер корпуса до минимума, требуемого для упаковки кристалла. Для микросхем, используемых в картах SmartMedia, применяют и оригинальную упаковку KGD (Known Good Die).

7.3. Энергонезависимая память

287

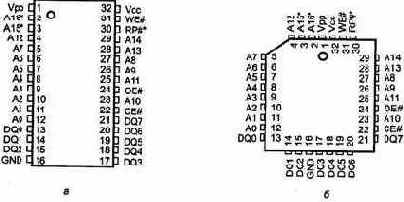

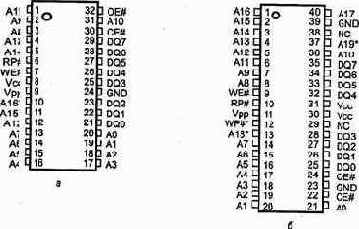

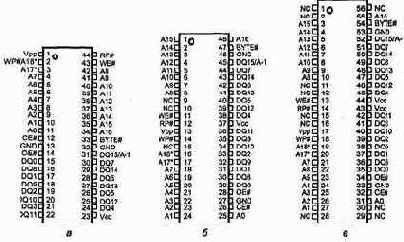

На рис. 7.20-7.22 приведено расположение выводов распространенных микросхем флэш-памяти (основной вариант цоколевки). Многие микросхемы имеют два варианта цоколевки для корпусов поверхностного монтажа — основной и зеркальный (реверсный). Это позволяет существенно упростить разводку печатных проводников (серпантином) при объединении большого количества микросхем в массивы флэш-памяти.

Рис. 7.20. Расположение выводов микросхем флэш-памяти с 8-битной организацией в корпусах DIP и PLCC: а — DIP-32, б — PLCC-32

Рис. 7.21. Расположение выводов микросхем флэш-памяти с 8-битной организацией в корпусах TSOP: а — TSOP-32, б — TSOP-40

288

Глава 7. Интерфейсы электронной памяти

Назначение сигналов микросхем флэш-памяти приведено в табл. 7.23; микросхемы разных изготовителей и моделей могут иметь не все из приведенных управляющих сигналов.

Таблица 7.23. Назначение сигналов микросхем флэш-памяти

к микросхеме, высокий уровень переводит микросхему в режим пониженного потребления. Доступ к микросхеме, имеющей два входа (СЕ1 # и СЕ2#), возможен при низком уровне на обоих входах

ОЕ# Output Enable — разрешение выходных буферов. Низкий уровень при низком уровне сигнала СЕ# разрешает чтение данных из микросхемы. Подача высокого (12В) напряжения во время подачи команды стирания или программирования позволяет модифицировать и Boot-блок (этот метод используется редко, поскольку требует не-ТТЛ сигнала)

WE# Write Enable — разрешение записи. Низкий уровень при низком уровне сигнала СЕ# разрешает запись и переводит выходные буферы в высокоимпедансное состояние независимо от сигнала ОЕ#. Временные диаграммы шинного цикла записи аналогичны обычной статической памяти, что позволяет подключать флэш-память непосредственно к системной шине процессора. Допустимы оба способа управления — как с помощью сигнала WE# на фоне низкого уровня СЕ#, так и наоборот. Минимальная длительность импульса записи совпадает со временем доступа

DQx Data Input/Output — двунаправленные линии шины данных. Время доступа при чтении отсчитывается от установки действительного адреса или сигнала СЕ# (в зависимости от того, что происходит позднее). Фиксация данных при записи происходит по положительному перепаду WE# или СЕ# в зависимости оттого, что происходит раньше

7.3. Энергонезависимая память

289

Сигнал Назначение

Ах Address — входные линии шины адреса. Линия А9 допускает подачу высокого (12В) напряжения (как и EPROM) для чтения кода производителя (А0=0) и устройства (А0=1), при этом на остальные адресные линии подается логический «О»

RP# Reset/Power Down, раньше обозначался PWD# (PowerDown). Низкий уровень (PWD#) сбрасывает регистр команд и переводит микросхемы в режим «глубокого сна»

(Deep Powerdown) с минимальным (доли микроампера) потреблением питания.

Перевод сигнала в высокий логический уровень «пробуждает» микросхему

(примерно за 0,3-0,8 мкс), после чего она переходит в режим чтения данных.

Подача высокого (12В) напряжения разрешает программирование даже

защищенного Boot-блока

WP# Write Protect — защита записи. При низком уровне WP* модификация Boot-блока или других блоков с установленным битом защиты возможна только при наличии высокого (12В) напряжения на входе RP*. При высоком уровне защита блоков игнорируется

RY/BY# Ready/Busy* — сигнал готовности (высокий уровень) микросхемы к очередной

операции программирования или стирания. Низкий уровень указывает на занятость управляющего автомата (WSM) выполнением операции стирания или программирования. Выход обычно не управляется сигналами ОЕ# и СЕ*. В микросхемах 28F016SA и выше выход имеет тип «открытый коллектор», запираемый по команде, и программируемое назначение

3/5* Сигнал, переключающий режим работы микросхемы в зависимости от питающего напряжения, введен для оптимизации быстродействия или потребления

Обозначение микросхем идя изделий лидеров в области разработки и производства флэш-памяти — фирм Intel и AMD — несколько отличаются. Остальные производители для своих изделий, по свойствам аналогичных, в основном придерживаются системы обозначений лидеров.

Обозначение микросхем флэш-памяти Intel начинается с признака 28F, за которым следует трехзначный код объема (табл. 7.24), а за ними — два символа технологии и архитектуры:

¦ В5, ВС, ВХ, BR - Boot Block с питанием 5 В;

¦ СЗ — Boot Block с питанием 3 В;

¦ F3 — Boot Block с питанием 3 В, повышенное быстродействие;

¦ J3 и J5 — StrataFlash (SA) с питанием 3 и 5 В соответственно;

¦ S3 и S5 — Flash File (SA) с питанием 3 и 5 В соответственно.

290________________________________ Глава 7. Интерфейсы электронной памяти

Для флэш-памяти AMD первая часть обозначения определяет тип и характеристики микросхем:

¦ Am29BDS — 1,8 В, считывание одновременно с записью, пакетный режим чтения;

¦ Am29DS — 1,8 В, считывание одновременно с записью;

¦ Am29SL- 1,8 В;

¦ Am29LV-3B;

¦ Am29DL — 3 В, считывание одновременно с записью;

¦ Am29BL — 3 В, пакетный режим чтения;

¦ Am29PL — 3 В, страничный режим чтения;

¦ AmSOLV - 3 В, UltraNAND;

¦ Am29F-5В.

Далее следует трехзначный код объема, за ним символ технологии изготовления (В, С или D), за которым следует символ архитектуры:

¦ Т — boot sector, верхний;,

¦ В — boot sector, нижний;

¦ Н — симметричная, защищен со старшим адресом;

¦ L — симметричная, защищен с младшим адресом;

¦ U (нет символа) — симметричная;

¦ J40 — число 100 %-годных блоков (только для UltraNAND).

Оставшаяся часть определяет параметры питания, быстродействие, тип корпуса, температурный диапазон и некоторые особенности.

Таблица 7.24. Популярные микросхемы флэш-памяти Обозначение Организация1

|

256 |

32Кх8ВЕ |

|

512 |

64Кх8ВЕ |

|

010 |

128Кх8ВЕ |

|

020 |

256 Кх 8 BE |

|

001 |

128Кх8ВВ |

|

002 |

256Кх8ВВ |

|

004 |

512Кх8ВВ, SA |

|

008 |

1Мх8ВВ, SA |

|

016 |

2 М х 8 ВВ, SA |

|

200 |

256Кх8/128Кх16ВВ |

|

400 |

512Кх8/256Кх16ВВ |

|

800 |

1024Кх8/512Кх16ВВ |

|

160 |

2Мх8/1 Mx16SA, ВВ |

|

320 |

4Mx8/2Mx16SA |

|

640 |

8Mx8/4Mx16SA |

7.3. Энергонезависимая память_________________________________________ 291

Флэш-память с интерфейсом PCMCIA (PC Card) оптимизирована для построения внешней памяти миниатюрных PC. Модуль флэш-памяти в формате PC Card имеет интерфейс дисков IDE (ATA) как на уровне электрических сигналов, так и по системе команд. Кроме собственно микросхем накопителя этот модуль обычно содержит управляющую микросхему программируемой логики. Флэш-память в стандарте PC Card логически является устройством внешней памяти. Ее не следует путать с похожей по виду памятью в формате Credit Card, которая является оперативной и вставляется в специальный (не PCMCIA) слот компьютера. Внешнюю память, в отличие от оперативной, в принципе можно вставлять и вынимать без перезагрузки ОС.

Организация и программирование флэш-памяти Intel

По организации и программированию можно выделить три поколения флэш-памяти Intel.

Микросхемы первого поколения (28F256,28F512,28F010,28F020) представляют собой единый массив памяти, стираемый целиком (bulk erase). Для выполнения стирания и записи микросхемы имеют внутренний регистр команд и управляющий автомат WSM (Write State Machine). Стирание и программирование флэш-памяти возможны только при подаче на вход VPP напряжения 12 В по командам, записываемым во внутренний регистр в шинном цикле записи по сигналу WE#.

Выполнение команд инициируется записью кодов команд во внутренний регистр, для чего процессор должен выполнить команду записи в память по адресу, принадлежащему области программируемой микросхемы флэш-памяти. На микросхему при этом должны прийти сигналы СЕ# (выбор) и WE# (запись). Последующие обращения к этой области как по записи (W), так и по чтению (R) должны соответствовать исполняемой команде (табл. 7.25).

В шинном цикле записи адрес (если он требуется для данной команды) фиксируется по спаду сигнала WE#, фиксация данных выполнения команды происходит по фронту WE#. Большинство команд подается безадресно (по любому адресу, принадлежащему данной микросхеме); команда верификации стирания и второй цикл команды программирования подаются по адресу требуемой ячейки. Результаты стирания и программирования считываются по адресу конкретной интересующей ячейки.

Ниже описано назначение команд.

¦ Read Memory — команда чтения данных, переводящая микросхему в режим чтения, совместимый по интерфейсу с EPROM.

¦ Read ID — команда чтения идентификаторов. В последующих шинных цик

лах чтения по адресу 0 считывается M_Id (Manufacturer Identifier — идентификатор производителя, 89h), по адресу 1 — D_Id (Device Identifier — идентификатор устройства, для микросхем 8F256,28F512,28F010,28F020 это B9h, B8h,B4h и BDh соответственно). Из этого режима микросхема выходит по записи любой другой действительной команды. Идентификаторы можно читать и путем подачи высокого напряжения на А9 (как и для EPROM).

292________________________________ Глава 7.. Интерфейсы электронной памяти

|

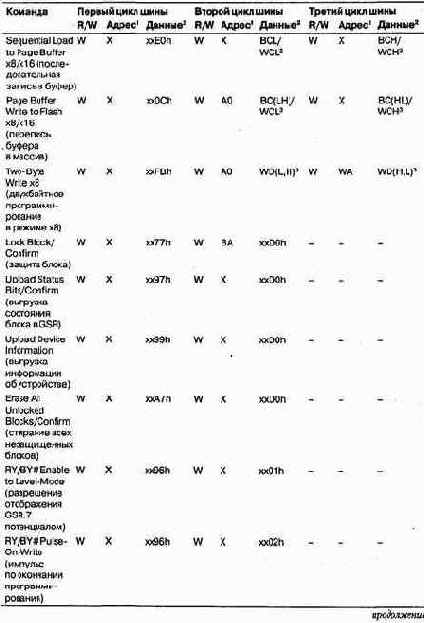

Таблица 7.25. Команды микросхем флэш-памяти Intel первого поколения |

|||||||

|

Команда |

Число |

Первый цикл шины1 |

Второй(третий)цикл шины1 |

||||

|

циклов шины |

R/W |

Адрес Данные R/W |

Адрес |

Данные |

|||

|

Read Memory |

1 |

W |

X |

ООп |

- |

- |

- |

|

Read ID |

3 |

W |

X |

90h |

R |

0(1) |

MJd (D_ld) |

|

Set-up Erase/Erase |

2 |

W |

X |

20h |

W |

X |

20h |

|

Erase Verify |

2 |

W |

ЕА |

АОп |

R |

X |

EVD |

|

Set-up Program/Program 2 |

W |

X |

40h |

W |

РА |

PD |

|

|

Program Verify |

2 |

W |

X |

COh |

R |

X |

PVD |

|

Reset |

2 |

W |

X |

FFh |

W |

X |

FFh |

¦ Set-up Erase/Erase — подготовка и собственно стирание. Внутренний цикл

стирания начинается по подъему сигнала WE# во втором шинном цикле и завершается по последующему шинному циклу записи или по внутреннему таймеру (Stop Timer). Последующей командой обычно является верификация стирания. Два шинных цикла записи, необходимые для выполнения команды, Снижают вероятность случайного стирания и позволяют отказаться от выполнения стирания посылкой команды Reset. Наличие внутреннего таймера позволяет не заботиться о точной выдержке времени для стирания, необходимо только выдержать минимальный интервал (около 10 мс). Перед стиранием все биты микросхемы должны быть предварительно запрограммированы в нули.

¦ Erase Verify — верификация стирания. Отличается от обычного считывания тем, что проверяемая ячейка ставится в более жесткие условия считывания для повышения достоверности контроля стирания. Между шинными циклами команды верификации должна быть пауза не менее 6 мкс. Алгоритм быстрого стирания (Quick-Erase) предусматривает предварительное обнуление всех ячеек (командами программирования) и выполнение команды стирания, сопровождаемой верификацией. Команды верификации последовательно выполняются для каждой ячейки микросхемы. Если результат считывания отличается от FFh, производится повторное стирание (длительностью 10 мс), и последующая верификация может начинаться с первой ранее не стертой ячейки. Если количество повторов стирания превышает 3 000, фиксируется ошибка стирания и микросхема признается негодной. Алгоритм позволяет выполнить полное стирание микросхемы менее чем за секунду.

¦ Set-up Program/Program — подготовка и собственно программирование.

Команда выполняется аналогично стиранию, но во втором шинном цикле пе

редается адрес и данные программируемой ячейки, а последующая выдержка

должна составлять не менее 10 мкс.

7.3. Энергонезависимая память_________________________________________ 293

¦ Program Verify— верификация программирования (аналогично верификации стирания), обычно следующая после команды программирования. Между шинными циклами команды верификации должна быть пауза не менее 6 икс. Алгоритм быстрого программирования (Quick-Pulse Programming) предусматривает формирование внутреннего цикла программирования длительностью 10 мкс с последующей верификацией. В случае несовпадения результата выполняется повторное программирование (до 25 раз для каждой ячейки), а если и это не

помогает — фиксируется отказ микросхемы.

¦ Reset — команда сброса, прерывающая команду программирования или стирания. Эта команда не меняет содержимое памяти; после нее требуется подача другой действительной команды.

По включении питания внутренний регистр команд обнуляется, что соответствует команде чтения, и микросхема работает как обычная микросхема PROM или EPROM. Это позволяет устанавливать микросхемы флэш-памяти вместо EPROM аналогичной емкости. При подаче на вход VPP низкого напряжения (0-6,5 В) стирание и программирование невозможны, и микросхема ведет себя как обычная EPROM.

Микросхемы второго поколения секторированы — ячейки группируются в блоки, допускающие независимое стирание (асимметричное разбиение — Boot Block и симметричное — Flash File). Длительная операция стирания одного блока может прерываться для считывания данных других блоков, что значительно повышает гибкость и производительность устройства. Микросхемы имеют более сложный внутренний управляющий автомат и в них введен регистр состояния, что позволяет разгрузить внешний процессор и программу от забот по отслеживанию длительности операций программирования и стирания, а также упростить эти процедуры.

В отличие от микросхем первого поколения, в шинном цикле записи адрес и данные фиксируются по положительному перепаду WE#. Низкий уровень дополнительного управляющего сигнала RP# (в первых версиях обозначался как PWD#) предназначен для перевода микросхемы в режим с минимальным потреблением.

В этом режиме модификация содержимого памяти невозможна. Соединение этого вывода в нормальном режиме (когда не требуется перезапись Boot-блока) с системным сигналом RESET* предохраняет микросхему от выполнения ложных команд, которые могут появиться в процессе подачи питания. Внутренние операции стирания и программирования выполняются после посылки соответствующих кодов во внутренний регистр команд. Команды приведены в табл. 7.26. Как и в первом поколении, этот регистр для большинства команд безадресный, но команды программирования и стирания посылаются по требуемому адресу ячейки (блока). Отработка операций внутренним управляющим автоматом отображается соответствующими битами регистра состояния SR (Status Register), по значению которых внешняя программа может получить информацию о результате выполнения и возможности посылки следующих команд. Чтение

294______________________________ Глава 7. Интерфейсы электронной памяти

регистра SR выполняется по специальной команде; есть и команда его очистки. Назначение бит регистра состояния описано ниже.

¦ SR. 7 — WSMS (Write State Machine Status) — состояние управляющего автомата:

• 0 — Busy (занят операцией стирания или программирования);

• 1 — Ready (свободен).

¦ SR.6—ESS (Erase Suspend Status) — состояние операции стирания:

• 0 — стирание завершено или выполняется;

• 1 — стирание приостановлено.

¦ SR. 5 — ES (Erase Status) — результат стирания блока:

• 0 — блок стерт успешно;

• 1 — ошибка стирания.

¦ SR. 4 — PS (Program Status) — результат программирования байта:

• 0 — байт записан успешно;

• 1 — ошибка записи.

¦ SR.3 — VPPS (VpP Status) — состояние VPP

во время программирования или стирания:

• 0 — напряжение было в норме;

• 1 — зафиксировано понижение напряжения, и операция прервана.

¦ S R [ 2 :0 ] — зарезервированы.

Таблица 7.26. Команды микросхем флэш-памяти Intel второго поколения

|

Команда |

Число |

Первый цикл шины1 |

Второй (третий) цикл шины1 |

||||

|

циклов шины |

R/W |

Адрес |

Данные |

R/W |

Адрес |

Данные |

|

|

Read Array/Reset |

1 |

W |

X |

FFh |

_ |

- |

_ |

|

Read ID |

3 |

W |

X |

90h |

R |

0(1) |

MJd |

|

(DJd) |

|||||||

|

Read Status Register |

2 |

W |

X |

70h |

R |

X |

SRD |

|

Clear Status Register |

1 |

W |

X |

50h |

- |

- |

- |

|

Erase Setup/Erase Confirm |

2 |

W |

ВА |

20h |

W |

BA |

DOh |

|

Erase Suspend/Erase |

2 |

W |

X |

BOh |

W |

X |

DOh |

|

Resume |

|||||||

|

Program Setup/Program |

2 |

W |

РА |

40h |

w |

PA |

PD |

|

Alternate Program Setup/ |

2 |

W |

РА |

10h |

w |

PA |

PD |

|

Program2 |

ства, SRD — данные, считанные из регистра состояния, РА и PD — адрес и данные программируемой

ячейки, В А— адрес блока.

2 Альтернативный код команды программирования; доступен для микросхем емкостью 2,4 и 8 Мбит.

7.3. Энергонезависимая память______ - ________________________________ 295

Ниже описано назначение команд.

¦ Read Array/Reset — чтение массива памяти (перевод в режим, совместимый

с EPROM) и прерывание операций стирания и программирования.

¦ Read ID — чтение идентификаторов производителя и устройства.

¦ Read Status Register — чтение регистра состояния.

¦ Clear Status Register — сброс регистра состояния.

¦ Erase Setup/Erase Conf i rm — подготовка и стирание блока. В отличие от

микросхем первого поколения, все внутренние операции, необходимые для

стирания (обнуление ячеек блока, стирание и верификация), выполняются

автоматически. При получении команды в регистре состояния устанавливает

ся признак занятости (SR. 7=0) и любая шинная операция чтения микросхемы будет передавать данные этого регистра. Внешняя программа, периодически опрашивая регистр состояния, дожидается окончания выполнения стирания (когда SR. 7=1). Результат стирания определяется по значению бит 3, 4, 5 (их нулевое значение соответствует успешному выполнению операции).

¦ Erase Suspend/Erase Resume — приостановка/продолжение стирания. Опе

рацию стирания блока (как самую длительную) можно приостановить для чте

ния данных из других блоков. После выполнения команды Erase Suspend (код BOh) необходимо дождаться признака приостановки стирания (SR. 6=1), после чего, подав команду Read Array, можно считывать данные другого блока. По окончании считывания подается команда Erase Resume (код DOh), которая продолжает процесс стирания и снова переводит микросхему в режим чтения регистра состояния.

¦ Program Setup/Program — подготовка и программирование ячейки. Эта команда выполняется аналогично подготовке и выполнению стирания, но не может быть приостановлена. Команда выполняет сразу и программирование, и верификацию.

Команды стирания блока и программирования можно подавать, только когда управляющий автомат свободен (бит SR. 7=1). Во время этих операций микросхема следит за уровнем напряжения VPP, и, если оно понижается до порога VPPLK) этот факт регистрируется в регистре состояния и операция прерывается. Также операция прерывается при понижении напряжения питания Vcc до 2,5 В.

При считывании регистра состояния его мгновенное значение фиксируется по спаду сигнала СЕ# или ОЕ# (самого позднего из них в шинном цикле считывания).

Программирование и стирание Boot-блока отличаются от операций с другими блоками тем, что для них требуется подача высокого потенциала VHH (не ТТЛ, а +12 В) на вход PWD# перед выдачей команды стирания или программирования и удержание его до успешного завершения операции.

Альтернативный способ — подача такого же потенциала, но на вход ОЕ# на время пар шинных циклов записи команд стирания или программирования. Попытка программирования Boot-блока без выполнения этих условий не удается, а в регистре состояния одновременно

296________________________________ Глава 7. Интерфейсы электронной памяти

устанавливаются единичные значения бит ES и PS, что индицирует попытку модификации защищенного блока.

Микросхемы Flash-file организованы в виде набора одинаковых блоков, равноправных (симметричных) по защите (Symmetrical Architecture, SA), Защита от модификации для 28F008SA может осуществляться только для всей микросхемы подачей низкого напряжения на вход VPP. По интерфейсу и командам микросхемы совпадают с микросхемами Boot Block (исключая специфику Boot-блока).

Архитектура микросхем 28F016SA существенно изменена, что значительно повышает производительность программирования (до 28,6 Мбайт/с в пакетном режиме) и обеспечивает поблочную защиту. Микросхема имеет два буфера данных для записи по 256 Кбайт. Флэш-память организована как 32 блока по 64 Кбайт, допускающих однобайтное или двухбайтное обращение. С каждым блоком связан собственный 8-битный регистр состояния блока BSRx (Block Status Register). Адреса регистров смещены относительно начального адреса блока на 2 или 1 для режимов обращения х8 или х!6 соответственно. Назначение бит BSR описано ниже.

¦ BSR. 7 — BS (Block Status) — состояние блока:

• 1 — готов;

• 0 — занят.

¦ B5R. 6 — BLS (Block-Lock Status) — состояние защиты блока:

• 1 — программирование и стирание запрещены;

• 0 — блок не защищен.

¦ BSR.5 — BOS (Block Operation Status) — состояние операции с блоком:

• 1 — операция завершена безуспешно;

• 0 — операция успешно завершена или выполняется.

¦ BSR. 4 — BOAS (Block Operation Abort Status) — состояние отмены операции с блоком:

• 1 — операция отменена;

• 0 — операция не отменялась.

¦ BSR. 3 — QS (Queue Status) — состояние очереди:

• 1 — очередь заполнена;

• 0 — очередь доступна.

¦ BSR. 2 -VPPS(VPP Status)- состояние VPP:

• 1 — обнаружен низкий уровень, операция прервана;

• 0 — VPP в норме.

¦ BSR[1:0] —зарезервированы.

7.3. Энергонезависимая память__________________________________ 297

Глобальный регистр состояния GSR ( Global Status Register) несет информацию о состоянии микросхемы в целом. К GSR можно обращаться по адресу, смещенному относительно начального адреса любого блока на 4 или 2 для режимов обращения х8 или х!6 соответственно. Назначение бит GSR описано ниже.

¦ GSR.7—W5MS (Write State Machine Status) — состояние автомата записи (и завершенности внутренних операций):

• 1 — занят;

• 0 — свободен.

¦ GSR.6 — 055 (Operation Suspend Status) — состояние приостановки операции:

• 1 — операция приостановлена;

• 0 — операция выполняется или завершена.

¦ G5R. 5 — DOS (Device Operation Status) — состояние операции (копирует бит регистра состояния текущего блока):

• 1 — операция завершена неудачно;

• 0 — операция успешно завершена или выполняется.

¦ G5R. 4 — DSS (Device Sleep Status) — состояние ожидания:

• 1 — ожидание (Sleep);

• 0 — нормальный режим.

¦ GSR.3 — QS (Queue Status) — состояние очереди:

• 1 — очередь заполнена;

• 0 — очередь доступна.

¦ GSR. 2 — PBAS (Page Buffer Available Status) — состояние буферов записи:

• 1 — есть свободный буфер;

• 0 — нет свободного буфера.

¦ GSR. 1 — PBS (Page Buffer Status) — состояние выбранного буфера записи:

• 1 — выбранный буфер свободен;

• 0 — буфер занят операцией с WSM.

¦ GSR.0— PBSS (Page Buffer Select Status) — номер выбранного буфера:

• 1 — выбран буфер 1;

• 0 — выбран буфер 0.

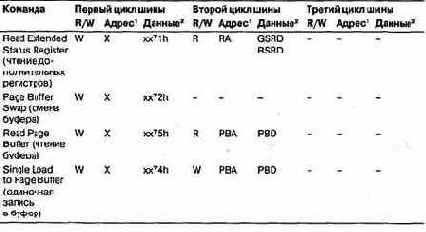

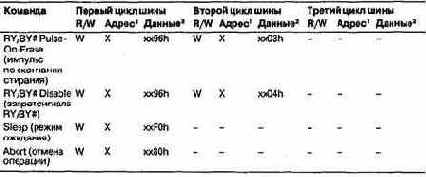

Для сохранения программной совместимости имеется безадресный регистр CSR (Compatible Status Register), полностью совпадающий с регистром состояния 28F008SA и микросхем с архитектурой Boot Block. Все команды этих микросхем доступны. Введены новые команды (табл. 7.27), обеспечивающие расширение функций. Ниже перечислены дополнительные возможности микросхем.

298________________________________ Глава 7. Интерфейсы электронной памяти

¦ Буферированное страничное программирование. Кроме обычного побайтного

или двухбайтного программирования возможно быстрое заполнение буфера

шинными циклами записи. Далее переписывание его содержимого (всего или

фрагмента) во флэш-память выполняется одной командой. Содержимое буфе

ра может быть считано после подачи соответствующей команды.

¦ Двухбайтное программирование при 8-битном использовании.

¦ Поддержка очереди команд позволяет при наличии свободного места в очере

ди подавать последующие команды стирания или программирования, не до

жидаясь освобождения автомата WSM. Признак готовности WSM установится только после выполнения всех команд очереди.

¦ Автоматическая запись из буфера во флэш-массив во время стирания другого

блока. Программная защита позволяет для любого блока установить бит защиты в специальную энергонезависимую область.

Запись и стирание защищенного блока может осуществляться только после снятия общей защиты записи по сигналу WP#. Сброс бита защиты блока осуществляется только при его успешном стирании или перезаписи.

¦ Стирание всех незащищенных блоков может выполняться одной командой.

¦ Программирование использования сигнала RY/BY*. Возможно разрешение

отображения бита готовности глобального регистра состояния, подачи им

пульсного сигнала по завершении программирования или стирания (на вы

бор), а также запрет его формирования.

¦ Перевод микросхемы в режим ожидания (Sleep) с пониженным потреблением В этом режиме возможно считывание состояния и получение команд.

Таблица 7.27. Дополнительные команды микросхем 28F016SA

7.3. Энергонезависимая память

299

300________________________________ Глава 7. Интерфейсы электронной памяти

Таблица 7.27 (продолжение)

1 BA - Block Address — адрес блокг, РВА - Page Buffer Address — адрес внутри буфера, RA - Extended

Register Address — адрес дополнительного регистра (BSRx или GSR), WA - Write Address — адрес во флэш-массиве. АО указывает на порядок следования байт в режиме х8{при низком уровне BYTE*):

О - сначала младший, затем старший; 1 - наоборот.

2 AD - Array Data — данные из массива, PBD - Page Buffer Data — данные буфера, WD (L,H) - Write

Data (Low, High) — данные для записи в массив, BSRD - BSR Data — информация регистра состояния блока, GSRD - GSR Data — информация глобального регистра состояния.

3 WC (L,H) - Word Count (Low, High) — счетчик слов. WCL-0 соответствует записи одного слова. Для буфера 256 байт WCH-0. BC (L,H) - Byte Count (Low, High) - счетчик байт. WCL-0 соответствует записи одного байта. Для буфера 256 байт WCH-0.

Микросхема 28F032SA представляет собой два параллельно соединенных кристалла 28F016SA в одном корпусе. Входы СЕ# одного из них соединены с выводами СЕО# и СЕ1 #, второго — с СЕО# и СЕ2#.

Третье поколение — современные микросхемы, выполненные по технологии SmartVoltage, допускают стирание и программирование при напряжении VPP как 12 В, так и 5 В.

В последнем случае эти операции занимают больше времени. Кроме того, операции чтения возможны при пониженном (3,3 и даже 2,7 В) напряжении питания Vcc, при этом снижается потребление, но увеличивается время доступа. Для управления защитой данных введен логический сигнал WP# (Write Protect). При его высоком уровне программирование и стирание защищенных блоков выполняются так же, как и остальных. При низком уровне WP# модификация защищенных блоков возможна только при наличии высокого (12 В) напряжения на входе RP#. Для полной защиты от стирания и программирования на вход VPP должен подаваться низкий логический уровень (или О В), а не 5 В, как у микросхем с программированием напряжением 12 В.

Настройка (оптимизация потребления и быстродействия) происходит по уровню напряжения на выводе Vcc по включении питания, переход на другое значение должен производиться через выключение питания.

Флэш-память фирмы AMD

Фирмой AMD выпускается несколько семейств микросхем флэш-памяти. Первые из них были близки по характеристикам к флэш-памяти Intel первого поколения

7.3. Энергонезависимая память_____________________________________________________________________ 301

(Bulk Erase, стирание и программирование 12 В): это Am28F256/512/ 010/020. В отличие от аналогичных микросхем Intel, Am28F256/512 не имели стоп^тайме-ра, что требовало точной выдержки при программировании и стирании. Следующим этапом были микросхемы Am28F256A/512A/010A/020A со встроенным алгоритмом программирования, отличающимся от алгоритма микросхем Intel второго поколения как последовательностью команд, так и способом определения момента окончания операций. Для защиты от случайного выполнения команды состоят из 3-6 шинных циклов, причем для них существенен и адрес (табл. 7.28). Состояние выполнения операций стирания или программирования определяется по результату данных, полученных в шинном цикле чтения по адресу ячейки, участвующей в операции (а не регистра состояния, как у Intel).

Для определения окон чания операций может использоваться метод Data# Polling или Toggle Bit. Метод Data# Polling основан на анализе бита D7 считанных данных. В начале выполнения внутреннего цикла он устанавливается инверсным по отношению к тому, что должно быть записано в ячейку. По успешном окончании операции он принимает желаемое значение (при стирании — 1). Метод Toggle Bit основан на анализе бита Об, который при каждом шинном цикле считывания во время выполнения операции меняет свое значение на противоположное. По окончании операции он остановится в каком-либо состоянии, при этом об успешности можно судить по биту 7. Единичное значение бита D5 — Exceeded Timing Limits — указывает на превышение допустимого времени выполнения операции.

Микросхемы семейства Am29Fxxx выполняют все операции при одном питающем напряжении 5 В и имеют секторированную структуру (Sector Erase), симметричную (аналогично Flash File) или несимметричную (Boot Block), с верхним (Т) и нижним (В) положением Boot-блока. С помощью программатора каждый сектор может быть защищен от модификации в целевой системе (в отличие от Intel способ установки и снятия защиты фирмой AMD широко не раскрывается). По расположению выводов и интерфейсу микросхемы соответствуют стандарту JEDEC для флэш-памяти с одним питающим напряжением. Микросхемы позволяют выполнять одновременное стирание группы секторов. Все эти микросхемы, кроме Am29F010, имеют возможность приостановки стирания сектора (Erase Suspend) для выполнения чтения других секторов, a Am29F080/016 позволяют еще и программировать байты во время приостановки стирания.

Таблица 7.28. Команды флэш-памяти Am29F010

|

Команда |

Reset/Read |

Autoselect |

Byte Program |

Chip Erase |

Sector Erase |

|

Количество |

3 |

3 |

4 |

6 |

6 |

|

циклов |

|||||

|

1-й цикл Addr |

5555h |

5555h |

5555h |

5555h |

5555h |

|

Data |

AAh |

AAh |

AAh |

AAh |

AAh |

|

2-й цикл Addr |

2AAAh |

2AAAh |

2AAAh |

2AAAh |

2AAAh |

|

Data |

55h |

55h |

55h |

55h |

55h |

продолжение &

|

302 |

|

Таблица 7.28 (продолжение) |

|||||

|

Команда Reset/Read |

Autoselect |

Byte Program |

Chip Erase |

Sector Erase |

|

|

3-й цикл Addr |

5555h |

5555h |

5555h |

5555И |

5555И |

|

Data |

FOh |

90h |

AOh |

80h |

80h |

|

4-й цикл Addr |

- |

XXOOh/XX01h |

PA1 |

5555И |

5555h |

|

Data |

01h/20h |

PD2 |

AAh |

AAh |

|

|

5-й цикл Addr |

- |

- |

- |

2AAAh |

2AAAh |

|

Data |

- |

- ¦ ¦¦ |

55h |

55h |

|

|

6-й цикл Addr |

- |

- |

- |

5555h |

SA3 |

|

Data |

- |

- |

- |

10h |

30h |

1PD - данные для записи в программируемую ячейку.

3SA - адрес стираемого сектора (значимы биты А16, А15 и А14).

В командах значение бит А15, А16 существенно только при задании адреса ячейки. Ниже описано назначение команд.

¦ Reset/Read — сброс и перевод в режим считывания массива. Производится

автоматически по включении питания и рри получении некорректной коман

ды (или адреса) в цепочке.

¦ Аи t о s е I е с t — чтение кодов идентификации производителя (А=0), устройства (А=1) или состояния защиты сектора (биты А16-А14 задают адрес сектора, А2-1, остальные биты адреса — нулевые). Результат считывания состояния защищенного сектора — Olh, незащищенного — OOh. Идентификаторы и состояние защиты могут быть считаны и путем подачи высокого напряжения на вход А9 в шинном цикле считывания.

¦ Byte Program — программирование байта. После четвертого цикла шины начинается внутреннее выполнение программирования, при этом чтение по адресу программируемой ячейки выводит биты состояния.

¦ Chi р Erase — стирание всех незащищенных секторов. На время выполнения стирания чтение по любому адресу (кроме адресов, принадлежащих защищенным секторам) выводит биты состояния.

¦ Sector Erase — стирание сектора или группы секторов.

Стирание начинается через 80 икс после окончания последнего шинного цикла цепочки. До этого момента можно посылать цепочки команд стирания других секторов, выполнение начнется через 80 мкс после окончания последней цепочки. Если среди указанных секторов имеется защищенный, его стирание не выполняется. На время выполнения стирания чтение по адресу любого из стираемых секторов (кроме защищенных) выводит биты состояния. Бит DQ3 — Sector Erase Timer — указывает на начало выполнения стирания сектора (очередную последовательность команд стирания сектора можно начинать, пока бит 3=0).

Следующим этапом стала секторированная флэш-память Am29LVxxx с одним питающим напряжением (3,0 В) для всех операций. У этих микросхем защита

7.3. Энергонезависимая память_________________________________________ 303

любого сектора также устанавливается с помощью программатора стандартной микросхемы EPROM.a также возможно временное снятие защиты в целевой системе. Кроме программной индикации окончания операции (биты 5-7, считанные по адресу ячейки), имеется и аппаратная (сигнал RY/BY*). Также имеется сигнал аппаратного сброса, переводящий в режим чтения.

Вышеперечисленные микросхемы имеют традиционную архитектуру NOR. От них значительно отличается микросхема Am30LV0064D — 64 Мбит (8 Мх8) с архитектурой UltraNAND, обеспечивающей быстрый последовательный доступ к данным выбранной страницы. Каждая страница имеет 512 байт данных и 16 дополнительных байт, используемых, например, для хранения ЕСС-кода. Для выбора страницы при чтении (загрузки во внутренний 528-байтный регистр) требуется около 7 мкс, после чего данные считываются последовательно со скоростью до 20 Мбайт/с (50 не/байт). Таким образом, среднее время на чтение одного байта составляет всего 65 не. Для записи данные (страница полностью или частично) загружаются в регистр с той же скоростью, после чего запись их в массив хранящих ячеек требует всего 200 мкс. Таким образом, среднее время на запись одного байта составляет всего 430 не — в 20 раз быстрее обычной (NOR) флэш-памяти (скорость записи 2,3 Мбайт/с).

Стирание выполняется блоками по 8 Кбайт за 2 мс (в обычной — 600 мс). Микросхем» питается от 3 В. Планируется достижение объема микросхемы до 1 Гбит. Надежность хранения — 10 лет, 104 циклов безошибочного программирования, более 106 циклов программирования с коррекцией ошибок. Применение — «твердые диски», цифровые камеры, диктофоны и т. п.

Флэш-память других фирм

Микросхемы флэш-памяти выпускаются многими фирмами. Они различаются по организации, интерфейсу, напряжению питания и программирования, методам защиты и другим параметрам. Лидеры в области разработки и производства флэш-памяти — фирмы AMD, Fujitsu Corporation, Intel Corporation и Sharp Corporation летом 1996 года приняли спецификацию CFI (Common Flash Memory Interface Specification), обеспечивающую совместимость разрабатываемого программного обеспечения с существующими и разрабатываемыми моделями флэш-памяти. Эта спецификация определяет механизм получения информации о производителе, организации, параметрах и возможных алгоритмах программирования микросхем флэш-памяти. Для этого микросхемы флэш-памяти должны поддерживать команду опроса QUERY. В первом шинном цикле в микросхему по адресу 55h посылается код 98h (микросхема может и игнорировать адрес, «отзываясь» только на код данных 98h). Во втором шинном цикле, адресованном к этой микросхеме, выполняется чтение данных .идентификационной структуры (на шину адреса микросхемы подается адрес интересующего байта структуры). Этими парами циклов структура может быть считана в произвольном порядке. Идентификационная структура содержит:

¦ ключ-признак наличия структуры — цепочка символов «QRY»;

¦ идентификатор (2 байта) первичного набора команд и интерфейса програм

мирования;

304________________________________ Глава 7. Интерфейсы электронной памяти

¦ указатель на таблицу параметров для программирования (и саму таблицу);

¦ идентификатор, указатель и таблицу параметров альтернативного набора

команд и интерфейса (если имеется);

¦ минимальные и максимальные значения напряжений питания (основного

и программирующего);

¦ значение тайм-аутов для операций стирания (блока и всей микросхемы) и за

писи (байта, слова, буфера);

¦ объем памяти;

¦ максимальное число байтов для многобайтной записи;

¦ описания независимо стираемых блоков.

Для перевода в режим чтения массива микросхемы должны воспринимать команду чтения массива Read Ar ray — запись кода FFh (FOh) по любому адресу в микросхеме.

Для большинства изделий справедливы тенденции, описанные при рассмотрении микросхем Intel и AMD, а именно — повышение объема, снижение напряжений питания и потребляемой мощности, повышение производительности и упрощение внешнего интерфейса для операций стирания и программирования. По интерфейсу программирования микросхемы, у которых в начальной части обозначения стоит число «28», как правило, близки к флэш-памяти Intel, а с числом «29» — к флэш-памяти AMD.

Микросхемы с буферированным программированием или страничной записью (Fast Page Write) могут не иметь в своей системе команд отдельной операции стирания сектора. Внутренняя операция стирания (и предварительного обнуления сектора) выполняется при страничном программировании.

Для защиты от случайного выполнения ключевые последовательности команд содержат от 2 до 6 шинных циклов, причем у них может быть важен и адрес (как в микросхемах AMD). Методы защиты секторов имеют различную как программную, так и аппаратную реализацию. Для временного снятия защиты используют различные способы, одним из которых является ключевая последовательность семи шинных циклов чтения.

Микросхемы флэш-памяти Micron совместимы с Intel и обозначаются аналогично, но начинаются с признака MT28F. Среди них есть и особенные, например: MT28F321P2FG - 2 М х 16 Page Flash Memory, MT28F322D18FH - 2 М х 16 Burst Flash Memory.

Фирма Silicon Storage Technology выпускает разнообразные микросхемы флэш-памяти с одним напряжением питания для всех операций. Их свойства можно определить по обозначению вида SST хх YY zzz — ttt, где хх — семейство:

¦ 28 — побайтное программирование, посекторное стирание;

¦ 29 — страничное программирование с прозрачным стиранием (команда стирания сектора отсутствует, внутренняя операция выполняется автоматически перед записью страницы в массив).

7.3. Энергонезависимая память________________________________________ 305

Элемент YY задает функциональный тип и напряжение питания:

¦ ЕЕ— EEPROM-совместимые, выполнение одной инструкции, Vcc = 5 В;

¦ LE - то же, что и ЕЕ, Vcc " 3 В;

¦ VE - то же, что и ЕЕ, Vcc - 2,7 В;

¦ SF— операции Super Flash Command Register, VCc = 5 В;

¦ IF-то же, что и SF, Vcc-3 В;

¦ W7-то же, что и SF, Vcc = 2,7 В;

¦ DM — Disk Media (для флэш-дисков, требует внешнего контроллера), Vcc = 5 В;

¦ LM — то же, что и DM, Vcc ~ 3 В;

¦ Ш-тоже, что и DM, VCC = 2,7B;

¦ PC — PCMCIA (интерфейс и протоколы), Vcc = 5 В.

Элемент zzz задает объем микросхемы:

¦ 572 - 512 Кбит (64 К х 8);

¦ 070-1Мбит(128Кх8);

¦ 040-4Мбит(512Кх8);

¦ 050 - 8 Мбит (1 М х 8);

¦ 016-16Мбит(2Мх8);

¦ 032 - 32 Мбит (4 М х 8).

Элемент ttt задает время доступа при чтении.

Микросхемы SST29EEQ10,29LE010 и 29VE010, часто применяемые в качестве носителя флэш-BIOS, организованы как 1024 страницы по 128 байт с программной и аппаратной защитой. Каждая страница может быть защищена независимо от других. Временные диаграммы стирания и программирования, а также необходимое напряжение программирования генерируются внутри микросхемы.Окончание операции определяется по алгоритму Toggle Bit или Data# Polling.

Аналогичные параметры имеют микросхемы 29ЕЕ011,29LE011,29VE011 фирмы Winbond.