Двунаправленный байтный режим — Byte Mode

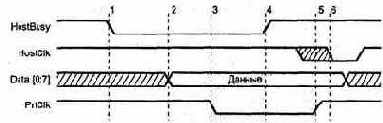

В этом режиме данные принимаются с использованием двунаправленного порта, у которого выходной буфер данных может отключаться установкой бита CR. 5=1. Как и предыдущие, режим является программно-управляемым — все сигналы квитирования анализируются и устанавливаются драйвером. Сигналы порта описаны в табл. 1.3, временные диаграммы — на рис. 1.2.

Таблица 1.3. Сигналы LPT-порта в байтном режима ввода-вывода

| Имя в байтном I/O Бит режиме |

| 1 14

17 16 10 |

Контакт Сигнал SPP

| lnit# Ack# |

Selectln* 1284Active

lnit# PtrClk

| 11 | Busy | PtrBusy | |||

| 12 | PE | AckDataReq1 | |||

| 13 | Select | Xflag1 | |||

| 15 | Error* | DataAvail*1 |

| 2-9 |

Data [0:7] Data [0:7]

Описание

О CR.O\ Импульс (низкого уровня) подтверждает прием байта в конце каждого цикла

О CR.1\ Сигнал квитирования. Низкий уровень означает готовность хоста принять байт; высокий уровень устанавливается по приему байта

О CR.3\ Высокий уровень указывает на обмен в режиме IEEE 1284 (в режиме SPP уровень низкий)

0 CR.2 Не используется; установлен высокий

уровень

1 SR.6 Устанавливается в низкий уровень

для индикации действительности данных на линиях Data [0:7]. В низкий уровень устанавливается в ответ на сигнал HostBusy

I SR-Д Состояние занятости прямого канала

I SR.5 Устанавливается ПУ для указания

на наличие обратного канала передачи

I SR.4 Флаг расширяемости

I SR.3 Устанавливается ПУ для указания

на наличие обратного канала передачи

I/O DR[0:7] Двунаправленный (прямой и обратный) канал данных

1:3. Стандарт IEEE 1284 • - 25

|

Рис. 1.2. Прием данных в байтном режиме

Фазы приема байта данных перечислены ниже.

1. Хост сигнализирует о готовности приема данных установкой низкого уровня

на линии HostBusy.

2. ПУ в ответ помещает байт данных на линии Data [0:7].

3. ПУ сигнализирует о действительности байта установкой низкого уровня на

линии PtrClk.

4. Хост устанавливает высокий уровень на линии HostBusy, указывая на занятость приемом и обработкой байта.

5. ПУ отвечает установкой высокого уровня на линии PtrClk,

6. Хост подтверждает прием байта импульсом HostClk.

Шаги 1-6 повторяются для каждого следующего байта. Квитирование осуществляется парой сигналов HostBusy и PtrClk; ПУ может и не использовать сигнал HostClk (это приглашение к выдаче следующего байта, напоминающее сигнал Ack# в интерфейсе Centronics). Побайтный режим позволяет поднять скорость обратного канала до скорости прямого канала в стандартном режиме. Однако он способен работать только на двунаправленных портах, которые раньше применялись в основном на малораспространенных машинах PS/2, но практически все современные порты можно сконфигурировать на двунаправленный режим (в настройках BIOS Setup - Bi-Di или PS/2).